Datasheet

MBI5120

# 16-Channel Constant Current LED Sink Driver

### **Features**

- 16 constant-current output channels

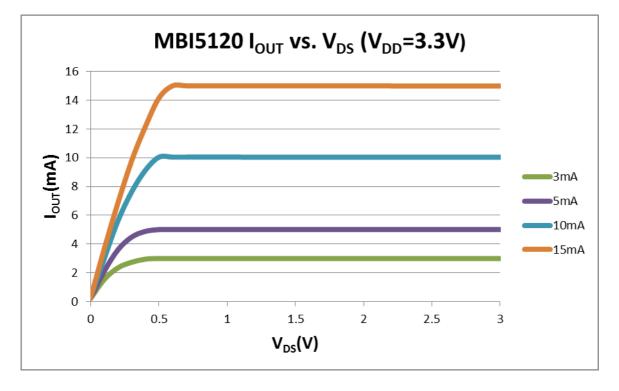

- Constant output current invariant to load voltage change: Constant output current range:

3-25mA@V<sub>DD</sub>=5V;

3-10mA@V<sub>DD</sub>=3.3V

- Excellent output current accuracy between channels: ±1.5% (typ.) and ±2% (max.) between ICs: ±1.5% (typ.) and ±3% (max.)

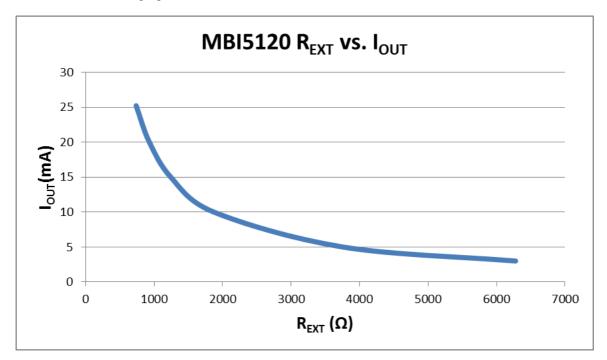

- Output current adjusted through an external resistor

- Fast response of output current,  $\overline{OE}$  (min.): 70ns with good uniformity between output channels

- Staggered delay of output

- 25MHz clock frequency

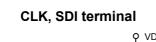

- Schmitt trigger input

- 3.3V/ 5V supply voltage

#### **Product Description**

With PrecisionDrive<sup>TM</sup> technology, MBI5120 is designed for LED displays which require to operate at low current and to match the luminous intensity of each channel. It provides supply voltage and accepts CMOS logic input at 3.3V and 5.0V to meet the trend of low power consumption. MBI5120 contains a serial buffer and data latches which convert serial input data into parallel output format. At MBI5120 output stage, sixteen regulated current ports are designed to provide uniform and constant current sinks for driving LEDs within a large range of V<sub>F</sub> variations.

MBI5120 provides users with great flexibility and device performance while using MBI5120 in their system design for LED display applications, e.g. LED panels. It accepts an input voltage range from 3V to 5.5V and maintains a constant current up from 1mA to 25mA determined by an external resistor, R<sub>ext</sub>, which gives users flexibility in controlling the light intensity of LEDs. MBI5120 guarantees to endure maximum 17V at the output port. The high clock frequency, 25 MHz, also satisfies the system requirements of high volume data transmission.

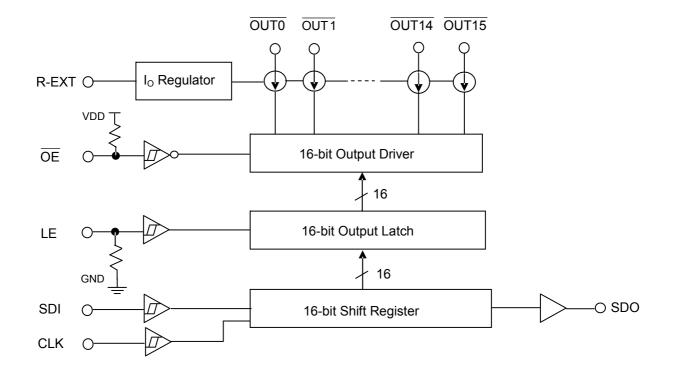

#### **Block Diagram**

# **Pin Configuration**

MBI5120GM

## **Terminal Description**

| Pin Name                                              | Function                                                                                                                                                                                                                  |

|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GND                                                   | Ground terminal for control logic and current sink                                                                                                                                                                        |

| SDI                                                   | Serial-data input to the shift register                                                                                                                                                                                   |

| CLK                                                   | Clock input terminal for data shift on rising edge                                                                                                                                                                        |

|                                                       | Data strobe input terminal                                                                                                                                                                                                |

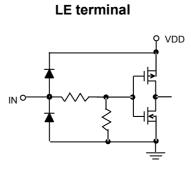

| LE                                                    | Serial data is transferred to the output latch<br>when LE is high. The data is latched when<br>LE goes low.                                                                                                               |

| $\overline{\text{OUT0}} \sim \overline{\text{OUT15}}$ | Constant current output terminals                                                                                                                                                                                         |

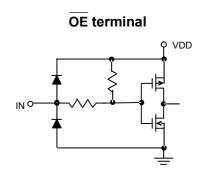

|                                                       | Output enable terminal                                                                                                                                                                                                    |

| ŌĒ                                                    | When $\overrightarrow{OE}$ (active) low $\overrightarrow{OUT0} \sim \overrightarrow{OUT15}$<br>are enabled. When $\overrightarrow{OE}$ high $\overrightarrow{OUT0} \sim \overrightarrow{OUT15}$ are turned OFF (blanked). |

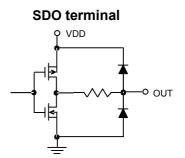

| SDO                                                   | Serial-data output to the following SDI of next driver IC                                                                                                                                                                 |

| R-EXT                                                 | Input terminal used to connect an external resistor for setting up output current for all output channels                                                                                                                 |

| VDD                                                   | 3.3V/5V supply voltage terminal                                                                                                                                                                                           |

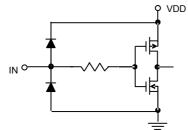

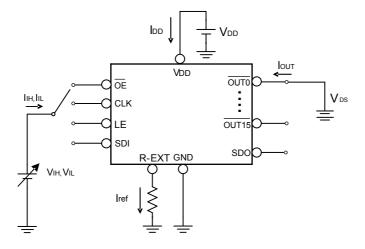

# **Equivalent Circuits of Inputs and Outputs**

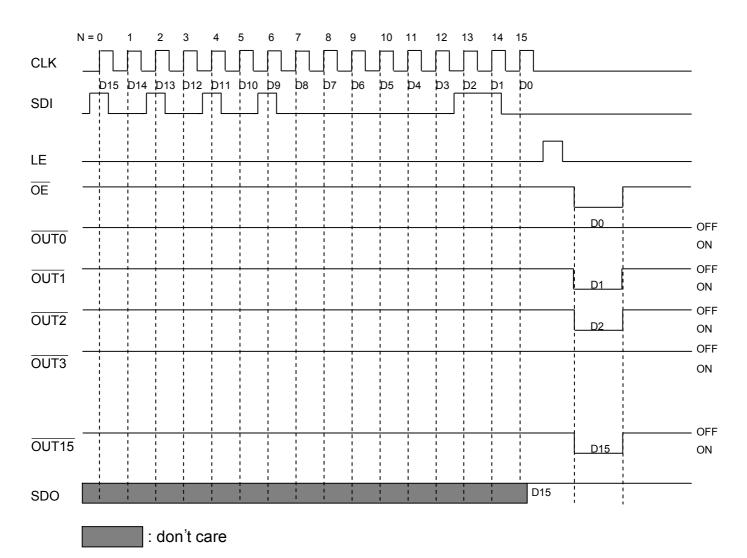

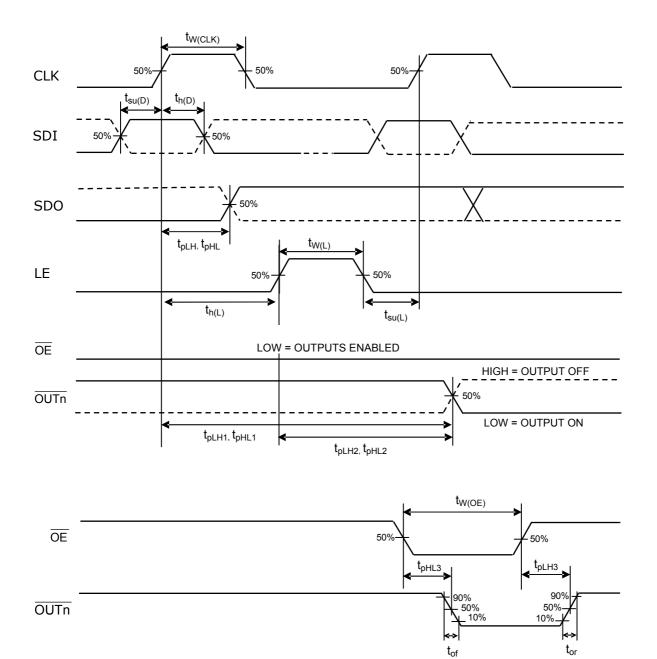

## **Timing Diagram**

# **Truth Table**

| CLK        | LE | ŌE | SDI              | OUT0 OUT7 OUT15                                                | SDO               |

|------------|----|----|------------------|----------------------------------------------------------------|-------------------|

|            | Н  | L  | D <sub>n</sub>   | Dn Dn - 7 Dn - 15                                              | D <sub>n-15</sub> |

| _ <b>^</b> | L  | L  | D <sub>n+1</sub> | No Change                                                      | D <sub>n-14</sub> |

|            | Н  | L  | D <sub>n+2</sub> | $\overline{Dn+2}$ $\overline{Dn-5}$ $\overline{Dn-13}$         | D <sub>n-13</sub> |

| T T        | х  | L  | D <sub>n+3</sub> | $\overline{Dn+2} \dots \overline{Dn-5} \dots \overline{Dn-13}$ | D <sub>n-13</sub> |

| , v        | х  | Н  | D <sub>n+3</sub> | Off                                                            | D <sub>n-13</sub> |

## Maximum Ratings

|                                               | Characteristic                              |                      | Symbol                          | Rating                     | Unit |

|-----------------------------------------------|---------------------------------------------|----------------------|---------------------------------|----------------------------|------|

| Supply Voltage                                |                                             |                      | V <sub>DD</sub>                 | 0~7.0                      | V    |

| Input Voltage (S                              | DI, CLK, LE, GCLK)                          |                      | V <sub>IN</sub>                 | -0.4~ V <sub>DD</sub> +0.4 | V    |

| Output Current                                |                                             |                      | I <sub>OUT</sub>                | +30                        | mA   |

| Sustaining Volta                              | ge at OUT Port                              |                      | V <sub>DS</sub>                 | -0.5~+17.0                 | V    |

| GND Terminal C                                | Current                                     |                      | I <sub>GND</sub>                | 480                        | mA   |

| Power Dissipation (On PCB, Ta= 25°C)* GM-type |                                             | P <sub>D</sub>       | 1.33                            | W                          |      |

| Thermal Resistance(On PCB, Ta= 25°C)* GM-type |                                             | R <sub>th(j-a)</sub> | 93.50                           | °C/W                       |      |

| Operating Junction Temperature                |                                             |                      | T <sub>j</sub> , <sub>max</sub> | 150**                      | °C   |

| Operating Ambi                                | ent Temperature                             |                      | T <sub>opr</sub>                | -40~+85                    | °C   |

| Storage Temperature                           |                                             |                      | T <sub>stg</sub>                | -55 ~ +150                 | °C   |

|                                               | HBM (MIL-STD-883G M<br>3015.8, Human Body M |                      | -                               | Class 3A<br>(6KV)          | -    |

| ESD Rating                                    | MM (ANSI/ ESD S5.2-2<br>Machine Mode)       | 009,                 | -                               | Class M4<br>(500V)         | -    |

\* The PCB size is 76.2mm\*114.3mm in simulation. Please refer to JEDEC JESD51.

\*\* Operation at the maximum rating for extended periods may reduce the device reliability; therefore, the suggested junction temperature of the device is under 125°C.

Note: The performance of thermal dissipation is strongly related to the size of thermal pad, thickness and layer numbers of the PCB. The empirical thermal resistance may be different from simulative value. Users should plan for expected thermal dissipation performance by selecting package and arranging layout of the PCB to maximize the capability.

# **Electrical Characteristics (V\_{DD} = 5.0V)**

| Characte                              | ristics    | Symbol                  | Co                                             | ndition                                        | Min.                 | Тур. | Max.                  | Unit |

|---------------------------------------|------------|-------------------------|------------------------------------------------|------------------------------------------------|----------------------|------|-----------------------|------|

| Supply Voltag                         | е          | V <sub>DD</sub>         | -                                              |                                                | 4.5                  | 5.0  | 5.5                   | V    |

| Output Voltage                        | 9          | V <sub>DS</sub>         |                                                | 5                                              | -                    | -    | 17                    | V    |

|                                       |            | Юит                     | Refer to "Test Circu<br>Electrical Character   |                                                | 3.0                  | -    | 25                    | mA   |

| Output Curren                         | t          | Ьн                      | SDO                                            |                                                | -                    | -1.0 | -                     | mA   |

|                                       |            | l <sub>ol</sub>         | SDO                                            |                                                | -                    | 1.0  | -                     | mA   |

|                                       | "H" level  | V <sub>IH</sub>         | Ta=-40~85°C                                    |                                                | $0.7 \times V_{DD}$  | -    | V <sub>DD</sub>       | V    |

| Input Voltage                         | "L" level  | VIL                     | Ta=-40~85°C                                    |                                                | GND                  | -    | 0.3 x V <sub>DD</sub> | V    |

| Output Leakag                         | je Current | Ьн                      | V <sub>DS</sub> =17.0V                         |                                                | -                    | -    | 0.5                   | μA   |

|                                       | SDO        | V <sub>OL</sub>         | I <sub>OL</sub> =+1.0mA                        |                                                | -                    | -    | 0.4                   | V    |

| Output Voltage                        | 300        | V <sub>OH</sub>         | I <sub>OH</sub> =-1.0mA                        |                                                | V <sub>DD</sub> -0.4 | -    | -                     | V    |

| Output Curren                         | ıt 1       | OUT1                    | $V_{DS}$ =1.0V                                 | V <sub>DS</sub> =1.0V R <sub>ext</sub> =1240 Ω |                      | 15   | -                     | mA   |

| Current Skew                          |            | dl <sub>out1</sub>      | I <sub>OL</sub> =15mA<br>V <sub>DS</sub> =1.0V | $R_{ext}$ =1240 $\Omega$                       | -                    | ±1.5 | ±2.5                  | %    |

| Current Skew                          |            | dl <sub>out2</sub>      | I <sub>OL</sub> =15mA<br>V <sub>DS</sub> =1.0V | $R_{ext}$ =1240 $\Omega$                       | -                    | ±1.5 | ±3.0                  | %    |

| Output Current vs<br>Output Voltage R |            | %/dV <sub>DS</sub>      | $V_{DS}$ within 1.0V                           | ′ and 3.0V                                     | -                    | ±0.1 | ±0.3                  | %/V  |

| Output Current vs<br>Supply Voltage R | i.         | %/dV <sub>DD</sub>      | $V_{DD}$ within 4.5V                           | ′ and 5.5V                                     | -                    | -    | ±1.0                  | %/V  |

| Pull-up Resist                        |            | R <sub>IN</sub> (up)    | ŌE                                             |                                                | 200                  | 460  | 700                   | KΩ   |

| Pull-down Res                         | sistor     | R <sub>IN</sub> (down)  | LE                                             |                                                | 200                  | 460  | 700                   | KΩ   |

|                                       | "OFF"      | I <sub>DD</sub> (off) 1 | R <sub>ext</sub> = Open , OL                   | R <sub>ext</sub> = Open , OUT0~OUT15 =Off      |                      | 2.7  | 3.7                   |      |

| Supply<br>Current                     | UFF        | I <sub>DD</sub> (off) 2 | $R_{ext}$ =1240 $\Omega$ , $\overline{O}$      | UT0~OUT15 =Off                                 | -                    | 9.7  | 10.7                  | mA   |

|                                       | "ON"       | I <sub>DD</sub> (on) 1  | $R_{ext}$ =1240 $\Omega$ , $\overline{O}$      | UT0~OUT15 =On                                  | -                    | 8.5  | 9.5                   |      |

## **Electrical Characteristics (V<sub>DD</sub>= 3.3V)**

| Characte                               | ristics   | Symbol                  | Cond                                           | dition                   | Min.                                      | Тур. | Max.                | Unit |

|----------------------------------------|-----------|-------------------------|------------------------------------------------|--------------------------|-------------------------------------------|------|---------------------|------|

| Supply Voltage                         | e         | V <sub>DD</sub>         | -                                              |                          | 3.0                                       | 3.3  | 3.6                 | V    |

| Output Voltage                         | 9         | V <sub>DS</sub>         |                                                | 5                        | -                                         | -    | 17                  | V    |

|                                        |           | I <sub>OUT</sub>        | Refer to "Test Circu<br>Electrical Character   | it for<br>istics"        | 3.0                                       | -    | 15                  | mA   |

| Output Curren                          | t         | I <sub>OH</sub>         | SDO                                            |                          | -                                         | -1.0 | -                   | mA   |

|                                        |           | I <sub>OL</sub>         | SDO                                            |                          | -                                         | 1.0  | -                   | mA   |

| Input Voltage                          | "H" level | V <sub>IH</sub>         | Ta=-40~85°C                                    |                          | $0.7 \mathrm{x} \mathrm{V}_{\mathrm{DD}}$ | -    | $V_{DD}$            | V    |

| input voltage                          | "L" level | V <sub>IL</sub>         | Ta=-40~85°C                                    |                          | GND                                       | -    | $0.3 \times V_{DD}$ | V    |

| Output Leakag                          | e Current | I <sub>OH</sub>         | V <sub>DS</sub> =17.0V                         |                          | -                                         | I    | 0.5                 | μA   |

|                                        | SDO       | V <sub>OL</sub>         | I <sub>OL</sub> =+1.0mA                        |                          | -                                         | -    | 0.4                 | V    |

| Output Voltage                         | 300       | V <sub>OH</sub>         | I <sub>OH</sub> =-1.0mA                        |                          | V <sub>DD</sub> -0.4                      | -    | -                   | V    |

| Output Curren                          | t 1       | I <sub>OUT1</sub>       | V <sub>DS</sub> =1.0V R <sub>ext</sub> =1240 Ω |                          | -                                         | 15   | -                   | mA   |

| Current Skew                           |           | dl <sub>OUT1</sub>      | I <sub>OL</sub> =15mA<br>V <sub>DS</sub> =1.0V | R <sub>ext</sub> =1240 Ω | -                                         | ±1.5 | ±2.5                | %    |

| Current Skew                           |           | dI <sub>OUT2</sub>      | I <sub>OL</sub> =15mA<br>V <sub>DS</sub> =1.0V | $R_{ext}$ =1240 $\Omega$ | -                                         | ±1.5 | ±3.0                | %    |

| Output Current vs<br>Output Voltage Re |           | %/dV <sub>DS</sub>      | V <sub>DS</sub> within 1.0V                    | and 3.0V                 | -                                         | ±0.1 | ±0.3                | %/V  |

| Output Current vs<br>Supply Voltage Re |           | %/dV <sub>DD</sub>      | $V_{DD}$ within 3.0V                           | and 3.6V                 | -                                         | -    | ±1.0                | %/V  |

| Pull-up Resiste                        | or        | R <sub>IN</sub> (up)    | ŌĒ                                             |                          | 200                                       | 460  | 700                 | KΩ   |

| Pull-down Res                          | istor     | R <sub>IN</sub> (down)  | LE                                             |                          | 200                                       | 460  | 700                 | KΩ   |

|                                        | "OFF"     | I <sub>DD</sub> (off) 1 | R <sub>ext</sub> =Open, OUT0~OUT15 =Off        |                          | -                                         | 2.5  | 3.5                 |      |

| Supply<br>Current                      | UFF       | I <sub>DD</sub> (off) 2 | R <sub>ext</sub> =1240Ω, OL                    | JT0~OUT15 =Off           | -                                         | 9.2  | 10.2                | mA   |

| Gunch                                  | "ON"      | I <sub>DD</sub> (on) 1  | $R_{ext}$ =1240 $\Omega$ , $\overline{OL}$     | JT0~OUT15 =On            | -                                         | 8.8  | 9.8                 |      |

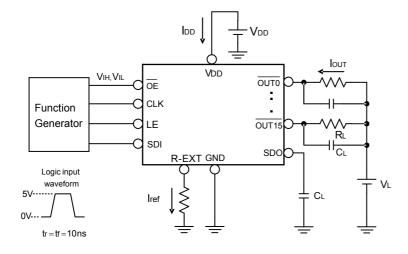

### **Test Circuit for Electrical Characteristics**

## Switching Characteristics ( $V_{DD}$ = 5.0V)

| Charac                                 | teristics                                 | Symbol              | Condition                                               | Min. | Тур. | Max. | Unit |

|----------------------------------------|-------------------------------------------|---------------------|---------------------------------------------------------|------|------|------|------|

|                                        | CLK-OUT 2n *                              | +                   |                                                         | -    | 37   | 52   | ns   |

|                                        | CLK-OUT 2n + 1*                           | t <sub>pLH1</sub>   |                                                         | -    | 35   | 50   | ns   |

|                                        | LE-OUT 2n                                 | +                   |                                                         | -    | 37   | 52   | ns   |

| Propagation Delay<br>Time ("L" to "H") | $LE-\overline{OUT 2n + 1}$                | t <sub>pLH2</sub>   |                                                         | -    | 35   | 50   | ns   |

|                                        | OE - OUT 2n                               | 4                   |                                                         | -    | 37   | 52   | ns   |

|                                        | $\overline{OE}$ - $\overline{OUT 2n + 1}$ | t <sub>pLH3</sub>   |                                                         | -    | 35   | 50   | ns   |

|                                        | CLK-SDO                                   | t <sub>pLH</sub>    |                                                         | -    | 25   | 35   | ns   |

|                                        | CLK-OUT 2n                                | 4                   |                                                         | -    | 27   | 37   | ns   |

|                                        | CLK-OUT 2n + 1                            | t <sub>pHL1</sub>   |                                                         | -    | 25   | 35   | ns   |

|                                        | LE-OUT 2n                                 | 4                   |                                                         | -    | 22   | 32   | ns   |

| Propagation Delay<br>Time ("H" to "L") | $LE-\overline{OUT 2n + 1}$                | t <sub>pHL2</sub>   |                                                         | -    | 20   | 30   | ns   |

|                                        | OE - OUT 2n                               | 4                   | V <sub>DD</sub> =5.0V<br>V <sub>DS</sub> =1.0V          | -    | 22   | 32   | ns   |

|                                        | $\overline{OE}$ - $\overline{OUT 2n + 1}$ | - t <sub>pHL3</sub> | $V_{IH} = V_{DD}$ $V_{IL} = GND$ $R_{ext} = 1240\Omega$ | -    | 20   | 30   | ns   |

|                                        | CLK-SDO                                   | t <sub>pHL</sub>    |                                                         | -    | 25   | 35   | ns   |

|                                        | CLK                                       | t <sub>w(CLK)</sub> | V <sub>L</sub> =4.0V                                    | 20   | -    | -    | ns   |

| Pulse Width                            | LE                                        | t <sub>w(L)</sub>   | R∟=200Ω<br>C∟=10pF                                      | 20   | -    | -    | ns   |

|                                        | OE **                                     | t <sub>w(OE)</sub>  |                                                         | 50   | 65   | -    | ns   |

| Hold Time for LE                       |                                           | t <sub>h(L)</sub>   |                                                         | 30   | -    | -    | ns   |

| Setup Time for LE                      |                                           | t <sub>su(L)</sub>  |                                                         | 5    | -    | -    | ns   |

| Hold Time for SDI                      |                                           | t <sub>h(D)</sub>   |                                                         | 5    | -    | -    | ns   |

| Setup Time for SDI                     |                                           | t <sub>su(D)</sub>  |                                                         | 3    | -    | -    | ns   |

| Maximum CLK Rise Time                  |                                           | tr                  |                                                         | -    | -    | 500  | ns   |

| Maximum CLK Fall Time                  |                                           | t <sub>f</sub>      |                                                         | _    | -    | 500  | ns   |

| SDO Rise Time                          |                                           | t <sub>r,SDO</sub>  |                                                         | -    | 10   | -    | ns   |

| SDO Fall Time                          |                                           | T <sub>f,SDO</sub>  |                                                         | -    | 10   | -    | ns   |

| Output Rise Time of                    | Output Ports                              | t <sub>or</sub>     |                                                         | -    | 35   | 45   | ns   |

| Output Fall Time of C                  | Output Ports                              | t <sub>of</sub>     |                                                         | -    | 40   | 50   | ns   |

\*The staggered delay between odd channels,  $\overline{OUT2n + 1}$  (e.g. OUT1, OUT3, OUT5, etc.) and even channels  $\overline{OUT2n}$  (e.g. OUT2, OUT4, OUT6, etc.) is 2ns. MBI5120 has a built-in staggered circuit to perform delay mechanism, by which the even and odd output ports will be turned on at a different time so that the instant current from the power line will be lowered.

\*\* With uniform output current.

## Switching Characteristics ( $V_{DD}$ = 3.3V)

| Charact                                | teristics                                 | Symbol              | Condition                                       | Min. | Тур. | Max. | Unit |

|----------------------------------------|-------------------------------------------|---------------------|-------------------------------------------------|------|------|------|------|

|                                        | CLK-OUT 2n *                              | +                   |                                                 | -    | 52   | 72   | ns   |

|                                        | CLK-OUT 2n + 1*                           | t <sub>pLH1</sub>   |                                                 | -    | 50   | 70   | ns   |

|                                        | LE-OUT 2n                                 | tuus                |                                                 | -    | 52   | 72   | ns   |

| Propagation Delay<br>Time ("L" to "H") | $LE-\overline{OUT 2n + 1}$                | t <sub>pLH2</sub>   |                                                 | -    | 50   | 70   | ns   |

|                                        | OE - OUT 2n                               |                     |                                                 | -    | 52   | 72   | ns   |

|                                        | $\overline{OE}$ - $\overline{OUT 2n + 1}$ | t <sub>pLH3</sub>   |                                                 | -    | 50   | 70   | ns   |

|                                        | CLK-SDO                                   | t <sub>pLH</sub>    |                                                 | -    | 35   | 45   | ns   |

|                                        | CLK-OUT 2n                                | 4                   |                                                 | -    | 27   | 37   | ns   |

|                                        | CLK-OUT 2n + 1                            | t <sub>pHL1</sub>   |                                                 | -    | 25   | 35   | ns   |

|                                        | LE-OUT 2n                                 |                     |                                                 | -    | 27   | 37   | ns   |

| Propagation Delay<br>Time ("H" to "L") | $LE-\overline{OUT 2n + 1}$                | t <sub>pHL2</sub>   |                                                 | -    | 25   | 35   | ns   |

|                                        | OE - OUT 2n                               | - t <sub>pHL3</sub> | V <sub>DD</sub> =3.3V<br>V <sub>DS</sub> =1.0V  | -    | 27   | 37   | ns   |

|                                        | $\overline{OE}$ - $\overline{OUT 2n + 1}$ |                     | V <sub>IH</sub> =V <sub>DD</sub>                | -    | 25   | 35   | ns   |

|                                        | CLK-SDO                                   | t <sub>pHL</sub>    | V <sub>IL</sub> =GND<br>R <sub>ext</sub> =1240Ω | -    | 35   | 45   | ns   |

|                                        | CLK                                       | t <sub>w(CLK)</sub> | V <sub>L</sub> =4.0V                            | 20   | -    | -    | ns   |

| Pulse Width                            | LE                                        | t <sub>w(L)</sub>   | R <sub>L</sub> =200Ω<br>C <sub>L</sub> =10 pF   | 20   | -    | -    | ns   |

|                                        | OE **                                     | t <sub>w(OE)</sub>  |                                                 | 60   | 75   | -    | ns   |

| Hold Time for LE                       |                                           | t <sub>h(L)</sub>   |                                                 | 30   | -    | -    | ns   |

| Setup Time for LE                      |                                           | t <sub>su(L)</sub>  |                                                 | 5    | -    | -    | ns   |

| Hold Time for SDI                      |                                           | t <sub>h(D)</sub>   |                                                 | 5    | -    | -    | ns   |

| Setup Time for SDI                     |                                           | t <sub>su(D)</sub>  |                                                 | 3    | -    | -    | ns   |

| Maximum CLK Rise Time                  |                                           | t <sub>r</sub>      |                                                 | -    | -    | 500  | ns   |

| Maximum CLK Fall Time                  |                                           | t <sub>f</sub>      |                                                 | -    | -    | 500  | ns   |

| SDO Rise Time                          |                                           | t <sub>r,SDO</sub>  |                                                 | -    | 10   | -    | ns   |

| SDO Fall Time                          |                                           | T <sub>f,SDO</sub>  |                                                 | -    | 10   | -    | ns   |

| Output Rise Time of (                  | Output Ports                              | t <sub>or</sub>     |                                                 | -    | 60   | 75   | ns   |

| Output Fall Time of O                  | utput Ports                               | t <sub>of</sub>     |                                                 | -    | 45   | 60   | ns   |

\*The staggered delay between odd channels,  $\overline{OUT2n + 1}$  (e.g. OUT1, OUT3, OUT5, etc.) and even channels  $\overline{OUT2n}$  (e.g. OUT2, OUT4, OUT6, etc.) is 2ns. MBI5020 has a built-in staggered circuit to perform delay mechanism, by which the even and odd output ports will be turned on at a different time so that the instant current from the power line will be lowered.

\*\* With uniform output current.

### **Test Circuit for Switching Characteristics**

### **Application Information**

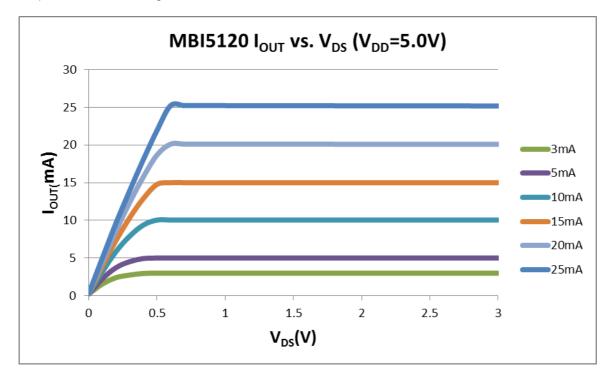

#### **Constant Current**

To design LED displays, MBI5120 provides nearly no variations in current from channel to channel and from IC to IC. This can be achieved by:

- 1) The maximum current variation between channels is less than  $\pm 2.5\%$ , and that between ICs is less than  $\pm 3\%$ .

- 2) In addition, the current characteristic of output stage is flat and users can refer to the figure as shown below. The output current can be kept constant regardless of the variations of LED forward voltages (V<sub>F</sub>). This performs as a perfection of load regulation.

### **Adjusting Output Current**

The output current of each channel ( $I_{OUT}$ ) is set by an external resistor,  $R_{ext}$ . The relationship between  $I_{OUT}$  and  $R_{ext}$  is shown in the following figure.

Also, the output current can be calculated from the equation:

$V_{R-EXT}$ =1.24V;  $I_{OUT}$ = $V_{R-EXT}$  \*(1/Rext)x15;  $R_{ext}$ =( $V_{R-EXT}/I_{OUT}$ )x15

where  $R_{ext}$  is the resistance of the external resistor connected to R-EXT terminal and  $V_{R-EXT}$  is the voltage of R-EXT terminal. The magnitude of current (as a function of R <sub>ext</sub>) is around 25mA at 744 $\Omega$  and 10mA at 1860 $\Omega$ .

### **MBI5120**

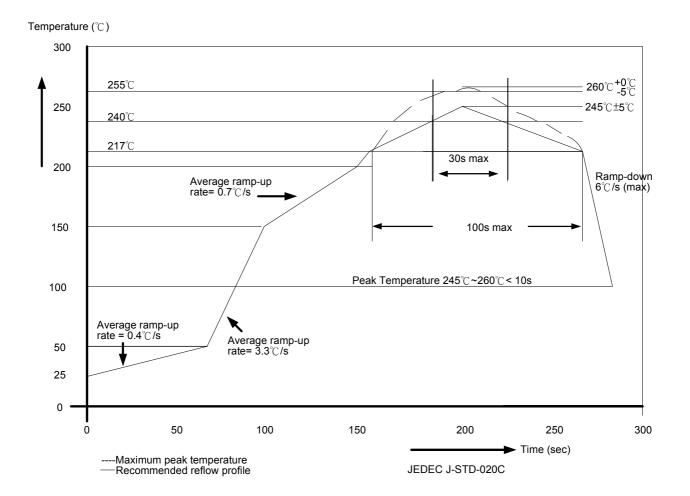

#### Soldering Process of "Pb-free & Green" Package Plating\*

Macroblock has defined "Pb-Free & Green" to mean semiconductor products that are compatible with the current RoHS requirements and selected 100% pure tin (Sn) to provide forward and backward compatibility with both the current industry-standard SnPb-based soldering processes and higher-temperature Pb-free processes. Pure tin is widely accepted by customers and suppliers of electronic devices in Europe, Asia and the US as the lead-free surface finish of choice to replace tin-lead. Also, it adopts tin/lead (SnPb) solder paste, and please refer to the JEDEC J-STD-020C for the temperature of solder bath. However, in the whole Pb-free soldering processes and materials, 100% pure tin (Sn) will all require from 245°C to 260°C for proper soldering on boards, referring to JEDEC J-STD-020C as shown below.

For managing MSL3 Package, it should refer to JEDEC J-STD-0 20C about floor life management & refer to JEDEC J-STD-033C about re-bake condition while IC's floor life exceeds MSL3 limitation.

| Package Thickness | Volume mm <sup>3</sup><br><350 | Volume mm <sup>3</sup><br>350-2000 | Volume mm <sup>3</sup><br>$\geq$ 2000 |

|-------------------|--------------------------------|------------------------------------|---------------------------------------|

| <1.6mm            | 260 +0 °C                      | 260 +0 °C                          | 260 +0 °C                             |

| 1.6mm – 2.5mm     | 260 +0 °C                      | 250 +0 °C                          | 245 +0 °C                             |

| ≧2.5mm            | 250 +0 °C                      | 245 +0 °C                          | 245 +0 °C                             |

\* For details, please refer to Macroblock's "Policy on Pb-free & Green Package".

# **MBI5120**

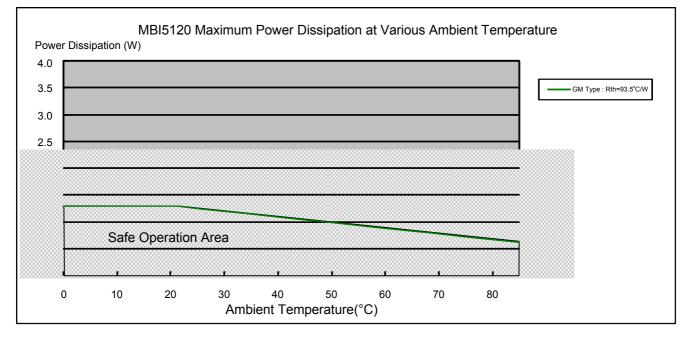

### Package Power Dissipation (P<sub>D</sub>)

The maximum allowable package power dissipation is determined as  $P_D(max)=(Tj-Ta)/R_{th(j-a)}$ . When 16 output

channels are turned on simultaneously, the actual package power dissipation is

$P_D(act)=(I_{DD}xV_{DD})+(I_{OUT}xDutyxV_{DS}x16)$ . Therefore, to keep  $P_D(act) \le P_D(max)$ , the allowable maximum output current as a function of duty cycle is:

$I_{OUT}=\{[(Tj-Ta)/R_{th(j-a)}]-(I_{DD}xV_{DD})\}/V_{DS}/Duty/16, where Tj=150^{\circ}C.$

| Condition: I <sub>OUT</sub> =25mA, 16 output channels active |                             |                    |  |  |

|--------------------------------------------------------------|-----------------------------|--------------------|--|--|

| Package                                                      | R <sub>th(j-a)</sub> (°C/W) | P <sub>D</sub> (W) |  |  |

| GM                                                           | 93.5                        | 1.33               |  |  |

The maximum power dissipation,  $P_D(max)=(Tj-Ta)/R_{th(j-a)}$ , decreases as the ambient temperature increases.

## **MBI5120**

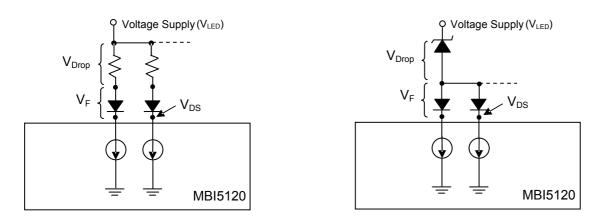

### Load Supply Voltage (V<sub>LED</sub>)

MBI5020 are designed to operate with V<sub>DS</sub> ranging from 0.4V to 0.8V (depending on I<sub>OUT</sub>=3~25mA) considering the package power dissipating limits. V<sub>DS</sub> may be higher enough to make  $P_{D(act)} > P_{D(max)}$  when V<sub>LED</sub>=5V and V<sub>DS</sub>=V<sub>LED</sub>-V<sub>F</sub>, in which V<sub>LED</sub> is the load supply voltage. In this case, it is recommended to use the lowest possible supply voltage or to set an external voltage reducer, V<sub>DROP</sub>.

A voltage reducer lets  $V_{DS}$ =( $V_{LED}$ - $V_{F}$ )- $V_{DROP}$ .

Resistors or Zener diode can be used in the applications as shown in the following figures.

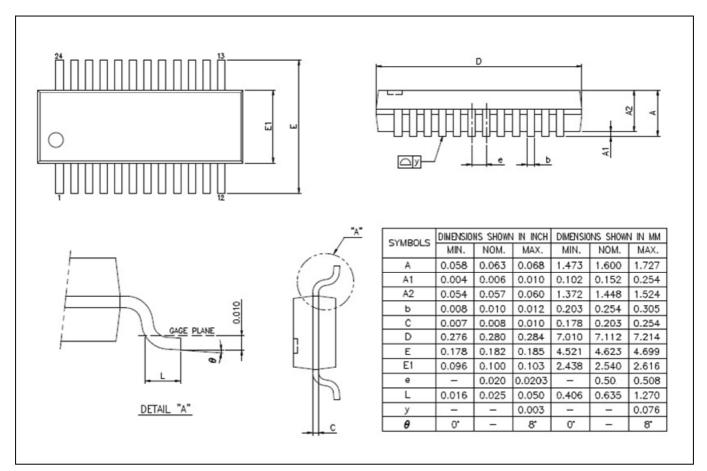

### **Package Outline**

MBI5120GM Outline Drawing

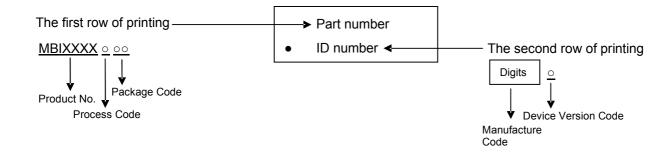

# **Product Top-mark Information**

## **Product Revision History**

| <b>Datasheet Version</b> | Device Version Code |

|--------------------------|---------------------|

| V1.00                    | A                   |

| V1.01                    | A                   |

| V1.02                    | A                   |

| V2.00                    | В                   |

| V2.01                    | В                   |

#### **Product Ordering Information**

| Part Number * | RoHS Package Type | Weight (g) |

|---------------|-------------------|------------|

| MBI5120GM-B   | mSSOP24L-100-0.5  | 0.079      |

\*Please place your order with the "Part Number" information on your purchase order (PO).

#### Disclaimer

Macroblock reserves the right to make changes, corrections, modifications, and improvements to their products and documents or discontinue any product or service without notice. Customers are advised to consult their sales representative for the latest product information before ordering. All products are sold subject to the terms and conditions supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

Macroblock's products are not designed to be used as components in device intended to support or sustain life or in military applications. Use of Macroblock 's products in components intended for surgical implant into the body, or other applications in which failure of Macroblock 's products could create a situation where personal death or injury may occur, is not authorized without the express written approval of the Managing Director of Macroblock. Macroblock will not be held liable for any damages or claims resulting from the use of its products in medical and military applications.

All text, images, logos and information contained on this document is the intellectual property of Macroblock. Unauthorized reproduction, duplication, extraction, use or disclosure of the above mentioned intellectual property will be deemed as infringement.