#### **General Description**

The MAX3100 universal asynchronous receiver transmitter (UART) is the first UART specifically optimized for small microcontroller-based systems. Using an SPITM/MICROWIRETM interface for communication with the host microcontroller ( $\mu$ C), the MAX3100 comes in a compact 16-pin QSOP. The asynchronous I/O is suitable for use in RS-232, RS-485, IR, and opto-isolated data links. IR-link communication is easy with the MAX3100's infrared data association (IrDA) timing mode.

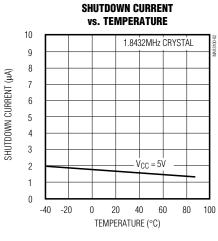

The MAX3100 includes a crystal oscillator and a baudrate generator with software-programmable divider ratios for all common baud rates from 300 baud to 230k baud. A software- or hardware-invoked shutdown lowers quiescent current to  $10\mu A$ , while allowing the MAX3100 to detect receiver activity.

An 8-word-deep first-in/first-out (FIFO) buffer minimizes processor overhead. This device also includes a flexible interrupt with four maskable sources, including address recognition on 9-bit networks. Two hardware-handshaking control lines are included (one input and one output).

The MAX3100 is available in 14-pin plastic DIP and small, 16-pin QSOP packages in the commercial and extended temperature ranges.

#### \_Applications

Handheld Instruments

Intelligent Instrumentation

UART in SPI Systems

Small Networks in HVAC or Building Control

Isolated RS-232/RS-485: Directly Drives Opto-Couplers

Low-Cost IR Data Links for Computers/Peripherals

#### Features

- ♦ Small TQFN and QSOP Packages Available

- **♦ Full-Featured UART:**

- —IrDA SIR Timing Compatible

- —8-Word FIFO Minimizes Processor Overhead at High Data Rates

- -Up to 230k Baud with a 3.6864MHz Crystal

- -9-Bit Address-Recognition Interrupt

- -Receive Activity Interrupt in Shutdown

- ♦ SPI/MICROWIRE-Compatible μC Interface

- **♦ Lowest Power:**

- -150µA Operating Current at 3.3V

- -10µA in Shutdown with Receive Interrupt

- ♦ +2.7V to +5.5V Supply Voltage in Operating Mode

- ♦ Schmitt-Trigger Inputs for Opto-Couplers

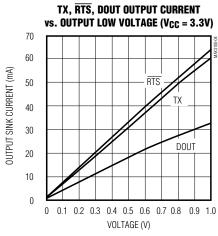

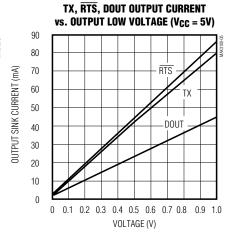

- ♦ TX and RTS Outputs Sink 25mA for Opto-Couplers

#### **Ordering Information**

| PART        | TEMP RANGE     | PIN-PACKAGE    |

|-------------|----------------|----------------|

| MAX3100CPD+ | 0°C to +70°C   | 14 Plastic DIP |

| MAX3100CEE+ | 0°C to +70°C   | 16 QSOP        |

| MAX3100EPD+ | -40°C to +85°C | 14 Plastic DIP |

| MAX3100EEE+ | -40°C to +85°C | 16 QSOP        |

| MAX3100ETG+ | -40°C to +85°C | 24 TQFN-EP*    |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package. EP = Exposed pad.

Typical Operating Circuit appears at end of data sheet.

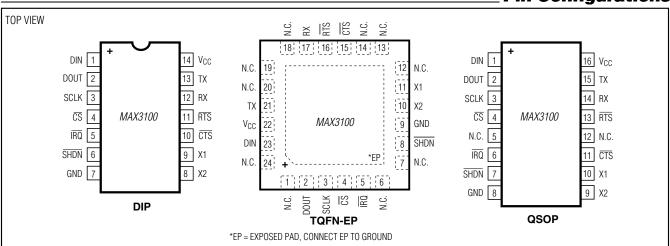

### **Pin Configurations**

SPI is a trademark of Motorola, Inc. MICROWIRE is a trademark of National Semiconductor Corp.

## **SPI/MICROWIRE-Compatible UART in QSOP-16**

#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> to GND+6V                                          | Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |

|--------------------------------------------------------------------|-------------------------------------------------------|

| Input Voltage to GND                                               | Plastic DIP (derate 10.00mW/°C above +70°C) 800mW     |

| (CS, SHDN, X1, CTS, RX, DIN, SCLK)0.3V to (V <sub>CC</sub> + 0.3V) | QSOP (derate 8.30mW/°C above +70°C)667mW              |

| Output Voltage to GND                                              | TQFN (derate 33.3mW/°C above +70°C)2666.7mW           |

| (DOUT, RTS, TX, X2)0.3V to (VCC + 0.3V)                            | Operating Temperature Ranges                          |

| ĪRQ0.3V to 6V                                                      | MAX3100C0°C to +70°C                                  |

| TX, RTS Output Current100mA                                        | MAX3100E40°C to +85°C                                 |

| X2, DOUT, IRQ Short-Circuit Duration                               | Storage Temperature Range65°C to +160°C               |

| (to V <sub>CC</sub> or GND)Indefinite                              | Lead Temperature (soldering, 10s)+300°C               |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = +2.7 \text{V to } +5.5 \text{V}, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted.}$  Typical values are measured at 9600 baud at  $T_A = +25 ^{\circ} \text{C.}$ )

| PARAMETER                                  | SYMBOL          | CONDITIO                                              | NS                     | MIN TYF                                 | MAX                   | UNITS |

|--------------------------------------------|-----------------|-------------------------------------------------------|------------------------|-----------------------------------------|-----------------------|-------|

| LOGIC INPUTS (DIN, SCI                     | LK, CS, SHDN    | Ī, CTS, RX)                                           |                        | 1                                       |                       |       |

| Input High Voltage                         | VIH             |                                                       |                        | 0.7 x Vcc                               |                       | V     |

| Input Low Voltage                          | VIL             |                                                       |                        |                                         | 0.3 x V <sub>CC</sub> | V     |

| Input Hysteresis                           | VHYST           | $V_{CC} = 3.3V$                                       |                        | 0.05 x <sup>v</sup>                     | √cc                   | V     |

| Input Leakage                              | IIL             |                                                       |                        |                                         | ±1                    | μΑ    |

| Input Capacitance                          | CIN             |                                                       |                        | 5                                       |                       | pF    |

| OSCILLATOR INPUT (X1                       | )               |                                                       |                        | •                                       |                       |       |

| Input High Voltage                         | VIH             |                                                       |                        | 0.7 x V <sub>CC</sub> V <sub>CC</sub> / | 2                     | V     |

| Input Low Voltage                          | VIL             |                                                       |                        | Vcc/                                    | 2 0.2 x Vcc           | V     |

| Input Current                              | l.s.            | $V_{X1} = 0V \text{ and } 5.5V$                       | Active mode            |                                         | 25                    | μΑ    |

| input Current                              | I <sub>IN</sub> | $V\chi_1 = 0V$ and 5.5V                               | Shutdown mode          |                                         | 2                     | 1 μΑ  |

| Input Capacitance                          | CIN             | $V_{X1} = 0V \text{ and } 5.5V$                       |                        | 5                                       |                       | pF    |

| OUTPUTS (DOUT, TX, R                       | ΓS)             |                                                       |                        |                                         |                       | •     |

| Output High Voltage                        | Voh             | ISOURCE = 5mA                                         |                        | V <sub>CC</sub> - 0.5                   |                       | V     |

| Output High Voltage                        | VOH             | ISOURCE = 25µA, TX only                               |                        | Vcc - 0.5                               |                       | V     |

| Output Low Voltage                         | VoL             | TX, $\overline{RTS}$ : $I_{SINK} = 25mA$              |                        |                                         | 0.9                   | V     |

| Output Low Voltage                         | VOL             | DOUT, TX, $\overline{RTS}$ : $I_{SINK} = 4r$          | mA                     |                                         | 0.4                   |       |

| Output Leakage                             | ILK             | DOUT only, $\overline{CS} = V_{CC}$                   |                        |                                         | ±1                    | μΑ    |

| Output Capacitance                         | Cout            |                                                       |                        | 5                                       |                       | pF    |

| IRQ OUTPUT (Open Drai                      | n)              |                                                       |                        | •                                       |                       | •     |

| Output Low Voltage                         | Vol             | ISINK = 4mA                                           |                        |                                         | 0.4                   | V     |

| Output Leakage                             | ILK             | V <sub>IRQ</sub> = 5.5V                               |                        |                                         | ±1                    | μΑ    |

| Output Capacitance                         | Соит            |                                                       |                        | 5                                       |                       | pF    |

| POWER REQUIREMENTS                         | S               |                                                       |                        |                                         |                       |       |

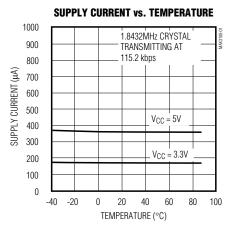

| V <sub>CC</sub> Supply Current in          | laa             | With 1.8432MHz crystal;                               | V <sub>CC</sub> = 5V   | 0.27                                    | 7 1                   | mA    |

| Normal Mode                                | Icc             | all other logic inputs are at $0V$ or $V_{CC}$        | V <sub>CC</sub> = 3.3V | 0.15                                    | 0.4                   | IIIA  |

| V <sub>CC</sub> Supply Current in Shutdown | Icc             | SHDN bit = 1 or SHDN = 0 logic inputs are at 0V or Vo | ,                      |                                         | 10                    | μΑ    |

| Supply Voltage                             | Vcc             |                                                       | 2.7                    | 5.5                                     | V                     |       |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = +2.7 \text{V to } +5.5 \text{V}, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted. Typical values are at } T_A = +25 ^{\circ}\text{C.})$

| PARAMETER                      | SYMBOL          | CONDITIONS                                     | MIN | TYP | MAX | UNITS |

|--------------------------------|-----------------|------------------------------------------------|-----|-----|-----|-------|

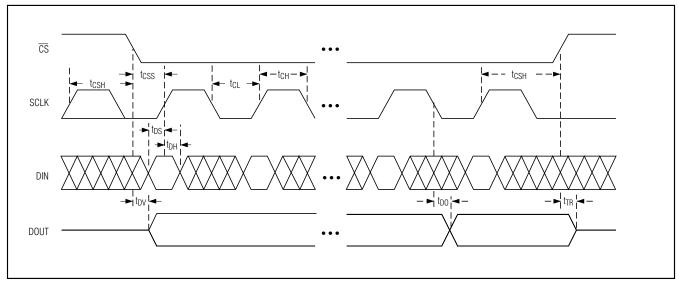

| AC TIMING (Figure 1)           | •               |                                                | -   |     |     | '     |

| CS Low to DOUT Valid           | t <sub>DV</sub> | C <sub>LOAD</sub> = 100pF                      |     |     | 100 | ns    |

| CS High to DOUT Tri-State      | ttr             | $C_{LOAD} = 100pF, R\overline{CS} = 10k\Omega$ |     |     | 100 | ns    |

| CS to SCLK Setup Time          | tcss            |                                                | 100 |     |     | ns    |

| CS to SCLK Hold Time           | tcsh            |                                                | 0   |     |     | ns    |

| SCLK Fall to DOUT Valid        | t <sub>DO</sub> | C <sub>LOAD</sub> = 100pF                      |     |     | 100 | ns    |

| DIN to SCLK Setup Time         | t <sub>DS</sub> |                                                | 100 |     |     | ns    |

| DIN to SCLK Hold Time          | tDH             |                                                | 0   |     |     | ns    |

| SCLK Period                    | tcp             |                                                | 238 |     |     | ns    |

| SCLK High Time                 | tch             |                                                | 100 |     |     | ns    |

| SCLK Low Time                  | tcL             |                                                | 100 |     |     | ns    |

| SCLK Rising Edge to CS Falling | tcso            | (Note 1)                                       | 100 |     |     | ns    |

| CS Rising Edge to SCLK Rising  | tCS1            | (Note 1)                                       | 200 |     |     | ns    |

| CS High Pulse Width            | tcsw            |                                                | 200 |     |     | ns    |

| Output Rise Time               | t <sub>r</sub>  | TX, RTS, DOUT: CLOAD = 100pF                   |     | 10  |     | ns    |

| Output Fall Time               | tf              | TX, RTS, DOUT, IRQ: CLOAD = 100pF              |     | 10  |     | ns    |

Note 1: tcso and tcs1 specify the minimum separation between SCLK rising edges used to write to other devices on the SPI bus and the CS used to select the MAX3100. A separation greater than tcso and tcs1 ensures that the SCLK edge is ignored.

Figure 1. Detailed Serial-Interface Timing

## **SPI/MICROWIRE-Compatible UART in QSOP-16**

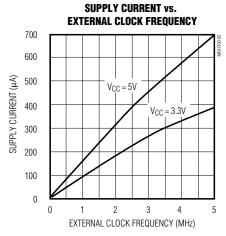

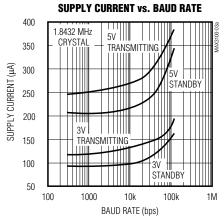

### Typical Operating Characteristics

$(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

## SPI/MICROWIRE-Compatible UART in QSOP-16

#### **Pin Description**

|       | PIN |                                           | NAME | FUNCTION                                                                                                                                                                                        |

|-------|-----|-------------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| QSOP  | DIP | TQFN-EP                                   | NAME | FUNCTION                                                                                                                                                                                        |

| 1     | 1   | 23                                        | DIN  | SPI/MICROWIRE Serial-Data Input. Schmitt-trigger input.                                                                                                                                         |

| 2     | 2   | 2                                         | DOUT | SPI/MICROWIRE Serial-Data Output. High impedance when $\overline{\text{CS}}$ is high.                                                                                                           |

| 3     | 3   | 3                                         | SCLK | SPI/MICROWIRE Serial-Clock Input. Schmitt-trigger input.                                                                                                                                        |

| 4     | 4   | 4                                         | CS   | Active-Low Chip-Select Input. DOUT goes high impedance when $\overline{\text{CS}}$ is high, $\overline{\text{IRQ}}$ , TX, and $\overline{\text{RTS}}$ are always active. Schmitt-trigger input. |

| 6     | 5   | 5                                         | ĪRQ  | Active-Low Interrupt Output. Open-drain interrupt output to microprocessor.                                                                                                                     |

| 7     | 6   | 8                                         | SHDN | Hardware-Shutdown Input. When shut down (SHDN = 0), the oscillator turns off immediately without waiting for the current transmission to end, reducing supply current to just leakage currents. |

| 8     | 7   | 9                                         | GND  | Ground                                                                                                                                                                                          |

| 9     | 8   | 10                                        | X2   | Crystal Connection. Leave X2 unconnected for external clock. See <i>Crystal-Oscillator Operation—X1</i> , X2 Connection section.                                                                |

| 10    | 9   | 11                                        | X1   | Crystal Connection. X1 also serves as an external clock input. See <i>Crystal-Oscillator Operation—X1</i> , X2 Connection section.                                                              |

| 11    | 10  | 15                                        | CTS  | General-Purpose Active-Low Input. Read via the CTS register bit; often used for RS-232 clear-to-send input (Table 1).                                                                           |

| 13    | 11  | 16                                        | RTS  | General-Purpose Active-Low Output. Controlled by the CTS register bit. Often used for RS-232 request-to-send output or RS-485 driver enable.                                                    |

| 14    | 12  | 17                                        | RX   | Asynchronous Serial-Data (receiver) Input. The serial information received from the modem or RS-232/RS-485 receiver. A transition on RX while in shutdown generates an interrupt (Table 5).     |

| 15    | 13  | 21                                        | TX   | Asynchronous Serial-Data (transmitter) Output                                                                                                                                                   |

| 16    | 14  | 22                                        | Vcc  | Positive Supply Pin (2.7V to 5.5V)                                                                                                                                                              |

| 5, 12 | _   | 1, 6, 7, 12,<br>13, 14, 18,<br>19, 20, 24 | N.C. | No Connection. Not internally connected.                                                                                                                                                        |

| _     |     | _                                         | EP   | Exposed Pad. Connect EP to ground or leave unconnected.                                                                                                                                         |

#### **Detailed Description**

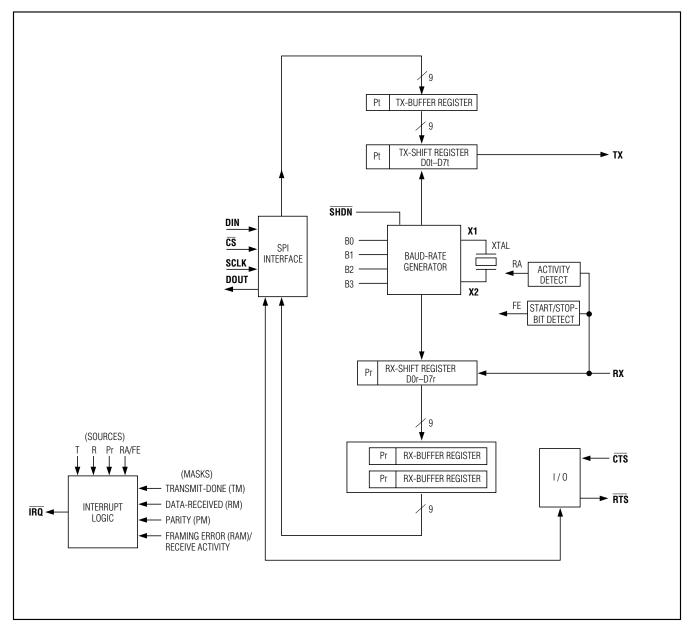

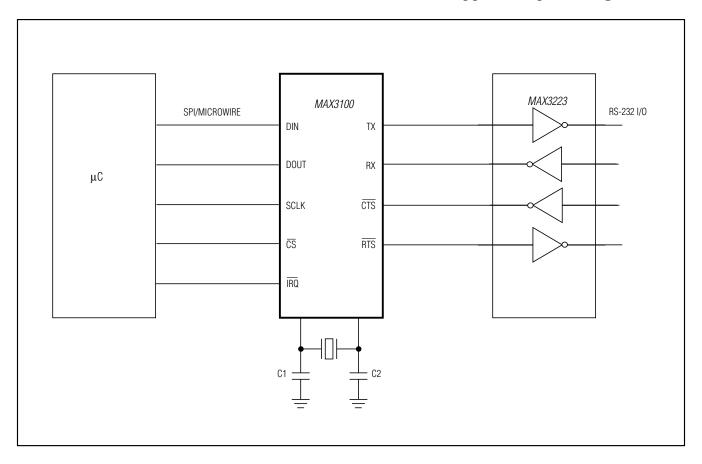

The MAX3100 universal asynchronous receiver transmitter (UART) interfaces the SPI/MICROWIRE-compatible, synchronous serial data from a microprocessor ( $\mu$ P) to asynchronous, serial-data communication ports (RS-232, RS-485, IrDA). Figure 2 shows the MAX3100 functional diagram.

The MAX3100 combines a simple UART and a baudrate generator with an SPI interface and an interrupt generator. Configure the UART by writing a 16-bit word to a write-configuration register, which contains the baud rate, data-word length, parity enable, and enable of the 8-word receive first-in/first-out (FIFO). The write configuration selects between normal UART timing and IrDA timing, controls shutdown, and contains 4 interrupt mask bits.

Transmit data by writing a 16-bit word to a write-data register, where the last 7 or 8 bits are actual data to be transmitted. Also included is the state of the transmitted parity bit (if enabled). This register controls the state of the RTS output pin. Received words generate an interrupt if the receive-bit interrupt is enabled.

Read data from a 16-bit register that holds the oldest data from the receive FIFO, the received parity data, and the logic level at the  $\overline{\text{CTS}}$  input pin. This register also contains a bit that is the framing error in normal operation and a receive-activity indicator in shutdown.

The baud-rate generator determines the rate at which the transmitter and receiver operate. Bits B0 to B3 in the write-configuration register determine the baud-rate divisor (BRD), which divides down the X1 oscillator frequency. The baud clock is 16 times the data rate (baud rate).

## SPI/MICROWIRE-Compatible UART in QSOP-16

Figure 2. Functional Diagram

The transmitter section accepts SPI/MICROWIRE data, formats it, and transmits it in asynchronous serial format from the TX output. Data is loaded into the transmit-

buffer register from the SPI/MICROWIRE interface. The MAX3100 adds start and stop bits to the data and clocks the data out at the selected baud rate (Table 7).

## SPI/MICROWIRE-Compatible UART in QSOP-16

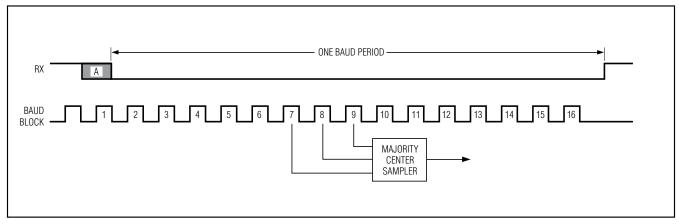

Figure 3. Start-Bit Timing

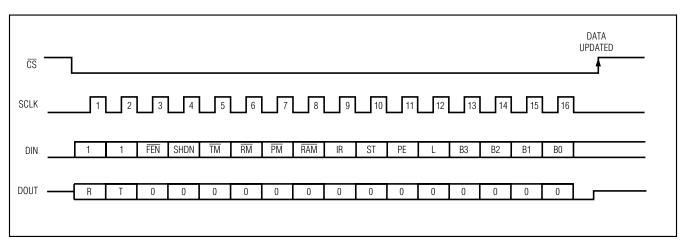

Figure 4. SPI Interface (Write Configuration)

The receiver section receives data in serial form. The MAX3100 detects a start bit on a high-to-low RX transition (Figure 3). An internal clock samples data at 16 times the data rate. The start bit can occur as much as one clock cycle before it is detected, as indicated by the shaded portion. The state of the start bit is defined as the majority of the 7th, 8th, and 9th sample of the internal 16x baud clock. Subsequent bits are also majority sampled. Receive data is stored in an 8-word FIFO. The FIFO is cleared if it overflows.

The on-board oscillator can use a 1.8432MHz or 3.6864MHz crystal, or it can be driven at X1 with a 45% to 55% duty-cycle square wave.

#### **SPI Interface**

The bit streams for DIN and DOUT consist of 16 bits, with bits assigned as shown in the MAX3100 Operations section. DOUT transitions on SCLK's falling edge, and DIN is latched on SCLK's rising edge (Figure 4). Most operations, such as the clearing of internal registers, are executed only on  $\overline{CS}$ 's rising edge. The DIN stream is monitored for its first two bits to tell the UART the type of data transfer being executed (Write Config, Read Config, Write Data, Read Data).

Only 16-bit words are expected. If  $\overline{CS}$  goes high in the middle of a transmission (any time before the 16th bit), the sequence is aborted (i.e., data does not get written to individual registers). Every time  $\overline{CS}$  goes low, a new 16-bit stream is expected. An example of a write configuration is shown in Figure 4.

## SPI/MICROWIRE-Compatible UART in QSOP-16

#### **MAX3100 Operations**

#### Write Operations

Table 1 shows write-configuration data. A 16-bit SPI/MICROWIRE write configuration clears the receive FIFO and the R, T, RA/FE, D0r–D7r, D0t–D7t, Pr, and Pt registers.  $\overline{\text{RTS}}$  and  $\overline{\text{CTS}}$  remain unchanged. The new configuration is valid on  $\overline{\text{CS}}$ 's rising edge if the transmit buffer is empty (T = 1) and transmission is over. If the latest transmission has not been completed, the registers are updated when the transmission is over (T = 0).

The write-configuration bits (FEN, SHDNi, IR, ST, PE, L, B3–B0) take effect after the current transmission is over. The mask bits (TM, RM, PM, RAM) take effect immediately after the 16th clock's rising edge at SCLK.

#### **Read Operations**

Table 2 shows read-configuration data. This register reads back the last configuration written to the

MAX3100. The device enters test mode if bit 0 = 1. In this mode, if  $\overline{CS} = 0$ , the  $\overline{RTS}$  pin acts as the 16x clock generator's output. This may be useful for direct baudrate generation (in this mode, TX and RX are in digital loopback).

Normally, the write-data register loads the TX-buffer register. To change the  $\overline{RTS}$  pin's state without writing data, set the  $\overline{TE}$  bit. Setting the  $\overline{TE}$  bit high inhibits the write command (Table 3).

Reading data clears the R bit and interrupt IRQ (Table 4).

#### **Register Functions**

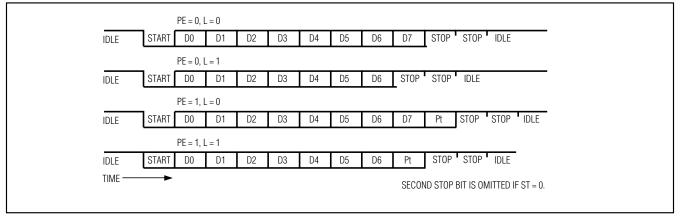

Table 5 shows read/write operation and power-on reset state (POR), and describes each bit used in programming the MAX3100. Figure 5 shows parity and word-length control.

#### Table 1. Write Configuration (D15, D14 = 1, 1)

| BIT  | 15 | 14 | 13  | 12    | 11 | 10 | 9  | 8   | 7  | 6  | 5  | 4 | 3  | 2  | 1  | 0  |

|------|----|----|-----|-------|----|----|----|-----|----|----|----|---|----|----|----|----|

| DIN  | 1  | 1  | FEN | SHDNi | TM | RM | PM | RAM | IR | ST | PE | L | ВЗ | B2 | B1 | В0 |

| DOUT | R  | Т  | 0   | 0     | 0  | 0  | 0  | 0   | 0  | 0  | 0  | 0 | 0  | 0  | 0  | 0  |

## Table 2. Read Configuration (D15, D14 = 0, 1)

| BIT  | 15 | 14 | 13  | 12    | 11 | 10 | 9  | 8   | 7  | 6  | 5  | 4 | 3  | 2  | 1  | 0    |

|------|----|----|-----|-------|----|----|----|-----|----|----|----|---|----|----|----|------|

| DIN  | 0  | 1  | 0   | 0     | 0  | 0  | 0  | 0   | 0  | 0  | 0  | 0 | 0  | 0  | 0  | TEST |

| DOUT | R  | Т  | FEN | SHDNo | TM | RM | PM | RAM | IR | ST | PE | L | ВЗ | B2 | B1 | В0   |

### Table 3. Write Data (D15, D14 = 1, 0)

| BIT  | 15 | 14 | 13 | 12 | 11 | 10    | 9   | 8  | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|------|----|----|----|----|----|-------|-----|----|-----|-----|-----|-----|-----|-----|-----|-----|

| DIN  | 1  | 0  | 0  | 0  | 0  | TE    | RTS | Pt | D7t | D6t | D5t | D4t | D3t | D2t | D1t | D0t |

| DOUT | R  | T  | 0  | 0  | 0  | RA/FE | CTS | Pr | D7r | D6r | D5r | D4r | D3r | D2r | D1r | D0r |

### Table 4. Read Data (D15, D14 = 0, 0)

| BIT  | 15 | 14 | 13 | 12 | 11 | 10    | 9   | 8  | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|------|----|----|----|----|----|-------|-----|----|-----|-----|-----|-----|-----|-----|-----|-----|

| DIN  | 0  | 0  | 0  | 0  | 0  | 0     | 0   | 0  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| DOUT | R  | Т  | 0  | 0  | 0  | RA/FE | CTS | Pr | D7r | D6r | D5r | D4r | D3r | D2r | D1r | D0r |

# SPI/MICROWIRE-Compatible UART in QSOP-16

## **Table 5. Bit Descriptions**

| BIT<br>NAME | READ/<br>WRITE | POR<br>STATE | DESCRIPTION                                                                                                                                                                                                                                                                                                   |

|-------------|----------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B0-B3       | W              | 0000         | Baud-Rate Divisor Select Bits. Sets the baud clock's value (Table 6).                                                                                                                                                                                                                                         |

| B0-B3       | r              | 0000         | Baud-Rate Divisor Select Bits. Reads the 4-bit baud clock value assigned to these registers.                                                                                                                                                                                                                  |

| CTS         | r              | No<br>change | Clear-to-Send-Input. Records the state of the $\overline{\text{CTS}}$ pin (CTS bit = 0 implies $\overline{\text{CTS}}$ pin = logic high).                                                                                                                                                                     |

| D0t-D7t     | W              | Х            | Transmit-Buffer Register. Eight data bits written into the transmit-buffer register. D7t is ignored when $L=1$ .                                                                                                                                                                                              |

| D0r–D7r     | r              | 00000000     | Eight data bits read from the receive FIFO or the receive register. These will be all 0s when the receive FIFO or the receive registers are empty. When $L=1$ , $D7r$ is always 0.                                                                                                                            |

| FEN         | W              | 0            | FIFO Enable. Enables the receive FIFO when $\overline{\text{FEN}} = 0$ . When $\overline{\text{FEN}} = 1$ , FIFO is disabled.                                                                                                                                                                                 |

| FEN         | r              | 0            | FIFO-Enable Readback. FEN's state is read.                                                                                                                                                                                                                                                                    |

| IR          | W              | 0            | Enables the IrDA timing mode when IR = 1.                                                                                                                                                                                                                                                                     |

| IR          | r              | 0            | Reads the value of the IR bit.                                                                                                                                                                                                                                                                                |

| L           | W              | 0            | Bit for setting the word length of the transmitted or received data. $L=0$ results in 8-bit words (9-bit words if $PE=1$ ), see Figure 5. $L=1$ results in 7-bit words (8-bit words if $PE=1$ ).                                                                                                              |

| L           | r              | 0            | Reads the value of the L bit.                                                                                                                                                                                                                                                                                 |

| Pt          | W              | Х            | Transmit-Parity Bit. This bit is treated as an extra bit that will be transmitted if PE = 1. To be useful in 9-bit networks, the MAX3100 does not calculate parity. If PE = 0, then this bit (Pt) is ignored in transmit mode (see the <i>Nine-Bit Networks</i> section).                                     |

| Pr          | r              | Х            | Receive-Parity Bit. This bit is the extra bit received if PE = 1. Therefore, PE = 1 results in 9-bit transmissions (L = 0). If PE = 0, then Pr is set to 0. Pr is stored in the FIFO with the receive data (see the <i>Nine-Bit Networks</i> section).                                                        |

| PE          | W              | 0            | Parity-Enable Bit. Appends the Pt bit to the transmitted data when PE = 1, and sends the Pt bit as written. No parity bit is transmitted when PE = 0. With PE = 1, an extra bit is expected to be received. This data is put into the Pr register. Pr = 0 when PE = 0. The MAX3100 does not calculate parity. |

| PE          | r              | 0            | Reads the value of the Parity-Enable bit.                                                                                                                                                                                                                                                                     |

| PM          | W              | 0            | Mask for Pr bit. $\overline{IRQ}$ is asserted if $\overline{PM} = 1$ and Pr = 1 (Table 6).                                                                                                                                                                                                                    |

| PM          | r              | 0            | Reads the value of the PM bit (Table 6).                                                                                                                                                                                                                                                                      |

| R           | r              | 0            | Receive Bit or FIFO Not Empty Flag. R = 1 means new data is available to be read from the receive register or FIFO.                                                                                                                                                                                           |

| RM          | W              | 0            | Mask for R bit. $\overline{IRQ}$ is asserted if $\overline{RM} = 1$ and R = 1 (Table 6).                                                                                                                                                                                                                      |

| RM          | r              | 0            | Reads the value of the RM bit (Table 6).                                                                                                                                                                                                                                                                      |

| RAM         | W              | 0            | Mask for RA/FE bit. $\overline{IRQ}$ is asserted if $\overline{RAM} = 1$ and RA/FE = 1 (Table 6).                                                                                                                                                                                                             |

| RAM         | r              | 0            | Reads the value of the RAM bit (Table 6).                                                                                                                                                                                                                                                                     |

| RTS         | W              | 0            | Request-to-Send Bit. Controls the state of the $\overline{\text{RTS}}$ output. This bit is reset on power-up (RTS bit = 0 sets the $\overline{\text{RTS}}$ pin = logic high).                                                                                                                                 |

## SPI/MICROWIRE-Compatible UART in QSOP-16

### **Table 5. Bit Descriptions (continued)**

| BIT<br>NAME | READ/<br>WRITE | POR<br>STATE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------|----------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RA/FE       | r              | 0            | Receiver-Activity/Framing-Error Bit. In shutdown mode, this is the RA bit. In normal operation, this is the FE bit. In shutdown mode, a transition on RX sets RA = 1. In normal mode, a framing error sets FE = 1. A framing error occurs if a zero is received when the first stop bit is expected. FE is set when a framing error occurs, and cleared upon receipt of the next properly framed character independent of the FIFO being enabled. When the device wakes up, it is likely that a framing error will occur. This error can be cleared with a write configuration. The FE bit is not cleared on a Read Data operation. When an FE is encountered, the UART resets itself to the state where it is looking for a start bit. |

| SHDNi       | w              | 0            | Software-Shutdown Bit. Enter software shutdown with a write configuration where SHDNi = 1. Software shutdown takes effect after $\overline{\text{CS}}$ goes high, and causes the oscillator to stop as soon as the transmitter becomes idle. Software shutdown also clears R, T, RA/FE, D0r–D7r, D0t–D7t, Pr, Pt, and all data in the receive FIFO. RTS and CTS can be read and updated while in shutdown. Exit software shutdown with a write configuration where SHDNi = 0. The oscillator restarts typically within 50ms of $\overline{\text{CS}}$ going high. RTS and CTS are unaffected. Refer to the <i>Pin Description</i> for hardware shutdown ( $\overline{\text{SHDN}}$ input).                                              |

| SHDNo       | r              | 0            | Shutdown Read-Back Bit. The read-configuration register outputs SHDNo = 1 when the UART is in shutdown. Note that this bit is not sent until the current byte in the transmitter is sent (T = 1). This tells the processor when it may shut down the RS-232 driver. This bit is also set immediately when the device is shut down through the SHDN pin.                                                                                                                                                                                                                                                                                                                                                                                 |

| ST          | W              | 0            | Transmit-Stop Bit. One stop bit will be transmitted when $ST = 0$ . Two stop bits will be transmitted when $ST = 1$ . The receiver only requires one stop bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| ST          | r              | 0            | Reads the value of the ST bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Т           | r              | 1            | Transmit-Buffer-Empty Flag. T = 1 means that the transmit buffer is empty and ready to accept another data word.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| TE          | W              | 0            | Transmit-Enable Bit. If $\overline{\text{TE}} = 1$ , then only the $\overline{\text{RTS}}$ pin will be updated on $\overline{\text{CS}}$ 's rising edge. The contents of $\overline{\text{RTS}}$ , Pt, and D0t-D7t transmit on $\overline{\text{CS}}$ 's rising edge when $\overline{\text{TE}} = 0$ .                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| TM          | W              | 0            | Mask for T bit. $\overline{IRQ}$ is asserted if $\overline{TM} = 1$ and T = 1 (Table 6).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TM          | r              | 0            | Reads the value of the $\overline{\text{TM}}$ bit (Table 6).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

Figure 5. Parity and Word-Length Control

#### **Interrupt Sources and Masks**

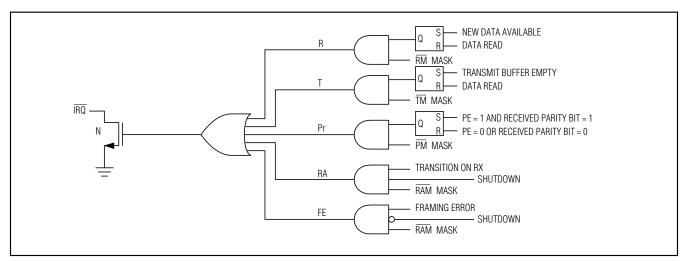

A Read Data operation clears the interrupt IRQ. Table 6 gives the details for each interrupt source. Figure 6

shows the functional diagram for the interrupt sources and mask blocks.

Table 6. Interrupt Sources and Masks—Bit Descriptions

| BIT<br>NAME | MASK<br>BIT | MEANING<br>WHEN SET                        | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------|-------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pr          | PМ          | Received parity bit = 1                    | The Pr bit reflects the value in the word currently in the receive-buffer register (oldest data available). The Pr bit is set when parity is enabled (PE = 1) and the received parity bit is 1. The Pr bit is cleared either when parity is not enabled (PE = 0), or when parity is enabled and the received bit is 0. An interrupt is issued based on the oldest Pr value in the receiver FIFO. The oldest Pr value is the next value that will be read by a Read Data operation. |

| R           | RM          | Data available                             | The R bit is set when new data is available to be read from the receive register/FIFO. FIFO is cleared when all data has been read. An interrupt is asserted as long as $R = 1$ and $\overline{RM} = 1$ .                                                                                                                                                                                                                                                                          |

| RA/FE       | RAM         | Transition on RX when in shutdown; framing | This is the RA (RX-transition) bit in shutdown, and the FE (framing-error) bit in operating mode. RA is set if there has been a transition on RX since entering shutdown. RA is cleared when the MAX3100 exits shutdown. IRQ is asserted when RA is set and RAM = 1.                                                                                                                                                                                                               |

| NAVE        | HAIVI       | error when not in<br>shutdown              | FE is determined solely by the currently received data, and is not stored in FIFO. The FE bit is set if a zero is received when the first stop bit is expected. FE is cleared upon receipt of the next properly framed character. IRQ is asserted when FE is set and RAM = 1.                                                                                                                                                                                                      |

| T           | TM          | Transmit buffer is empty                   | The T bit is set when the transmit buffer is ready to accept data. $\overline{IRQ}$ is asserted low if $\overline{IM} = 1$ and the transmit buffer becomes empty. This source is cleared on $\overline{CS}$ 's rising edge during a Read Data operation. Although the interrupt is cleared, T may be polled to determine transmit-buffer status.                                                                                                                                   |

Figure 6. Interrupt Sources and Masks Functional Diagram

## SPI/MICROWIRE-Compatible UART in QSOP-16

Table 7. Baud-Rate Selection Table\*

| В3 | BA<br>B2 | UD<br>B1 | В0  | DIVISION<br>RATIO | BAUD<br>RATE<br>(fosc =<br>1.8432MHz) | BAUD<br>RATE<br>(fosc =<br>3.6864MHz) |

|----|----------|----------|-----|-------------------|---------------------------------------|---------------------------------------|

| 0  | 0        | 0        | 0** | 1                 | 115.2k**                              | 230.4k**                              |

| 0  | 0        | 0        | 1   | 2                 | 57.6k                                 | 115.2k                                |

| 0  | 0        | 1        | 0   | 4                 | 28.8k                                 | 57.6k                                 |

| 0  | 0        | 1        | 1   | 8                 | 14.4k                                 | 28.8k                                 |

| 0  | 1        | 0        | 0   | 16                | 7200                                  | 14.4k                                 |

| 0  | 1        | 0        | 1   | 32                | 3600                                  | 7200                                  |

| 0  | 1        | 1        | 0   | 64                | 1800                                  | 3600                                  |

| 0  | 1        | 1        | 1   | 128               | 900                                   | 1800                                  |

| 1  | 0        | 0        | 0   | 3                 | 38.4k                                 | 76.8k                                 |

| 1  | 0        | 0        | 1   | 6                 | 19.2k                                 | 38.4k                                 |

| 1  | 0        | 1        | 0   | 12                | 9600                                  | 19.2k                                 |

| 1  | 0        | 1        | 1   | 24                | 4800                                  | 9600                                  |

| 1  | 1        | 0        | 0   | 48                | 2400                                  | 4800                                  |

| 1  | 1        | 0        | 1   | 96                | 1200                                  | 2400                                  |

| 1  | 1        | 1        | 0   | 192               | 600                                   | 1200                                  |

| 1  | 1        | 1        | 1   | 384               | 300                                   | 600                                   |

<sup>\*</sup>Standard baud rates shown in bold

#### **Clock-Oscillator Baud Rates**

Bits B0–B3 of the write-configuration register determine the baud rate. Table 7 shows baud-rate divisors for given input codes, as well as the given baud rate for 1.8432MHz and 3.6864MHz crystals. Note that the baud rate = crystal frequency / 16x division ratio.

#### **Shutdown Mode**

In shutdown, the oscillator turns off to reduce power dissipation (I<sub>CC</sub> < 10µA). The MAX3100 enters shutdown in one of two ways: by a software command (SHDNi bit = 1) or by a hardware command (SHDN = logic low). The hardware shutdown is effective immediately and will immediately terminate any transmission in progress. The software shutdown, requested by setting SHDNi bit = 1, is entered upon completing the transmission of the data in both the transmit register and the transmit-buffer register. The SHDNo bit is set when the MAX3100 enters shutdown (either hardware or software). The microcontroller ( $\mu$ C) can monitor the SHDNo bit to determine when all data has been transmitted, and shut down any external circuitry (such as RS-232 transceivers) at that time.

Shutdown clears the receive FIFO, R, A, RA/FE, D0r–D7r, Pr, and Pt registers and sets the T bit high. Configuration bits ( $\overline{RM}$ ,  $\overline{TM}$ ,  $\overline{PM}$ ,  $\overline{RAM}$ , IR, ST, PE, L, B0-3, and RTS) can be modified when SHDNo = 1 and CTS can also be read. Even though RA is reset upon entering shutdown, it will go high when any transitions are detected on the RX pin. This allows the UART to monitor activity on the receiver when in shutdown.

The command to power up (SHDNi = 0) turns on the oscillator when  $\overline{\text{CS}}$  goes high if  $\overline{\text{SHDN}}$  pin = logic high, with a start-up time of about 25ms. This is done through a write configuration, which clears all registers but  $\overline{\text{RTS}}$  and  $\overline{\text{CTS}}$ . Since the crystal oscillator typically requires 25ms to start, the first received characters will be garbled, and a framing error may occur.

### Applications Information

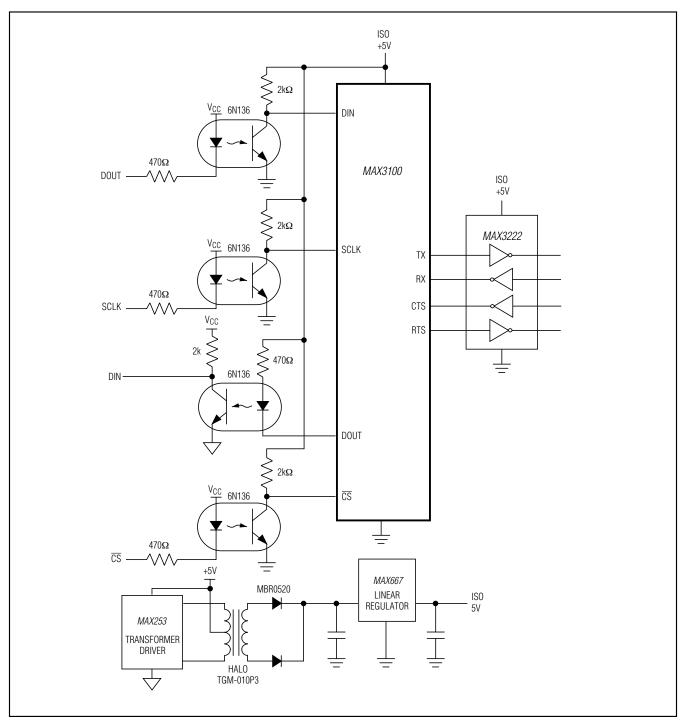

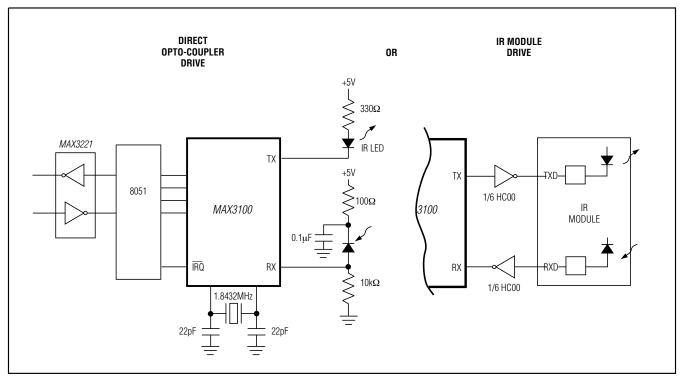

#### **Driving Opto-Couplers**

Figure 7 shows the MAX3100 in an isolated serial interface. The MAX3100 Schmitt-trigger inputs are driven directly by opto-coupler outputs. Isolated power is provided by the MAX253 transformer driver and linear regulator shown. A significant feature of this application is that the opto-coupler's skew does not affect the asynchronous serial output's timing. Only the set-up and hold times of the SPI interface need to be met.

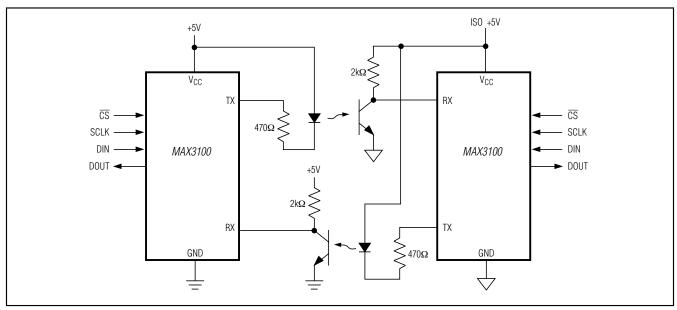

Figure 8 shows a bidirectional opto-isolated interface using only two opto-isolators. Over 81% power savings is realized using IrDA mode due to its 3/16-wide baud periods.

#### Crystal-Oscillator Operation— X1, X2 Connection

The MAX3100 includes a crystal oscillator for baud-rate generation. For standard baud rates, use a 1.8432MHz or 3.6864MHz crystal. The 1.8432MHz crystal results in lower operating current; however, the 3.6864MHz crystal may be more readily available in surface mount.

Ceramic resonators are low-cost alternatives to crystals and operate similarly, though the "Q" and accuracy are lower. Some ceramic resonators are available with integral load capacitors, which can further reduce cost. The tradeoff between crystals and ceramic resonators is in initial frequency accuracy and temperature drift. The total error in the baud-rate generator should be kept below 1% for reliable operation with other systems. This is accomplished easily with a crystal, and in most cases can be achieved with ceramic resonators. Table 8 lists the different types of crystals and resonators and their suppliers.

<sup>\*\*</sup>Default baud rate

# SPI/MICROWIRE-Compatible UART in QSOP-16

Figure 7. Driving Optocouplers

## SPI/MICROWIRE-Compatible UART in QSOP-16

Figure 8. Bidirectional Opto-Isolated Interface

**Table 8. Component and Supplier List**

| DESCRIPTION                     | FREQUENCY<br>(MHz) | TYPICAL<br>C1, C2 (pF) | SUPPLIER                | PART<br>NUMBER | PHONE<br>NUMBER |

|---------------------------------|--------------------|------------------------|-------------------------|----------------|-----------------|

| Through-Hole Crystal (HC-49/U)  | 1.8432             | 25                     | ECS International, Inc. | ECS-18-13-1    | (913) 782-7787  |

| Through-Hole<br>Resonator       | 1.8432             | 47                     | Murata North America    | CSA1.84MG      | (800) 831-9172  |

| Through-Hole Crystal (HC-49/US) | 3.6864             | 33                     | ECS International, Inc. | ECS-36-18-4    | (913) 782-7787  |

| SMT Crystal                     | 3.6864             | 39                     | ECS International, Inc. | ECS-36-20-5P   | (913) 782-7787  |

| SMT Resonator                   | T Resonator 3.6864 |                        | AVX/Kyocera             | PBRC-3.68B     | (803) 448-9411  |

This oscillator supports parallel-resonant mode crystals and ceramic resonators, or can be driven from an external clock source. Internally, the oscillator consists of an inverting amplifier with its input, X1, tied to its output, X2, by a bias network that self-biases the inverter at approximately V<sub>CC</sub> / 2. The external feedback circuit, usually a crystal, from X2 to X1 provides 180° of phase shift, causing the circuit to oscillate. As shown in the standard application circuit, the crystal or resonator is connected between X1 and X2, with the load capacitance for the crystal being the series combination of C1 and C2. For example, a 1.8432MHz crystal with a spec-

ified load capacitance of 11pF would use capacitors of 22pF on either side of the crystal to ground. Series-resonant mode crystals have a slight frequency error, typically oscillating 0.03% higher than specified series-resonant frequency, when operated in parallel mode.

It is **very important** to keep crystal, resonator, and load-capacitor leads and traces as short and direct as possible. The X1 and X2 trace lengths and ground tracks should be tight, with no other intervening traces. This helps minimize parasitic capacitance and noise pickup in the oscillator, and reduces EMI. Minimize capacitive loading on X2 to minimize supply current.

## SPI/MICROWIRE-Compatible UART in QSOP-16

The MAX3100 X1 input can be driven directly by an external CMOS clock source. The trip level is approximately equal to V<sub>CC</sub> / 2. No connection should be made to X2 in this mode. If a TTL or non-CMOS clock source is used, AC couple with a 10nF capacitor to X1. The peak-to-peak swing on the input should be at least 2V for reliable operation.

#### 9-Bit Networks

The MAX3100 supports a common multidrop communication technique referred to as 9-bit mode. In this mode, the parity bit is set to indicate a message that contains a header with a destination address. The MAX3100 parity mask can be set to generate interrupts for this condition. Operating a network in this mode reduces the processing overhead of all nodes by enabling the slave controllers to ignore most message traffic. This can relieve the remote processor to handle more useful tasks.

In 9-bit mode, the MAX3100 is set up with 8 bits plus parity. The parity bit in all normal messages is clear, but is set in an address-type message. The MAX3100 parity-interrupt mask is enabled to generate an interrupt on high parity. When the master sends an address message with the parity bit set, all MAX3100 nodes issue an interrupt. All nodes then retrieve the received byte to compare to their assigned address. Once addressed, the node continues to process each received byte. If the node was not addressed, it ignores all message traffic until a new address is sent out by the master.

Figure 9. IrDA Timing

The parity/9th-bit interrupt is controlled only by the data in the receive register, and is not affected by data in the FIFO, so the most effective use of the parity/9th-bit interrupt is with FIFO disabled. With the FIFO disabled, received nonaddress words can be ignored and not even read from the UART.

#### **SIR IrDA Mode**

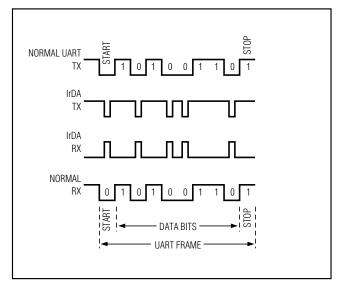

The MAX3100's IrDA mode can be used to communicate with other IrDA SIR-compatible devices, or to reduce power consumption in opto-isolated applications.

In IrDA mode, a bit period is shortened to 3/16 of a baud period (1.6µs at 115,200 baud) (Figure 9). A data zero is transmitted as a pulse of light (TX pin = logic low, RX pin = logic high).

In receive mode, the RX signal's sampling is done halfway into the transmission of a high level. The sampling is done once, instead of three times, as in normal mode. The MAX3100 ignores pulses shorter than approximately 1/16 of the baud period. The IrDA device that is communicating with the MAX3100 must be set to transmit pulses at 3/16 of the baud period. For compatibility with other IrDA devices, set the format to 8-bit data, one stop, no parity.

#### IrDA Module

The MAX3100 was optimized for direct optocoupler drive, whereas IrDA modules contain inverting buffers. Invert the RX and TX outputs as shown in Figure 10.

#### 8051 Example: IrDA to RS-232 Converter

Figure 10 shows the MAX3100 with an 8051  $\mu$ C. This circuit receives IrDA data and outputs standard RS-232 data. Although the 8051 contains an internal UART, it does not support IrDA or high-speed communications. The MAX3100 can easily interface to the 8051 to support these high-performance communications modes. The 8051 does not have an SPI interface, so communication with the MAX3100 is accomplished with port pins and a short software routine (Figure 12a).

The software routine polls the  $\overline{\text{IRQ}}$  output to see if data is available from the MAX3100 UART. It then shifts the data out, using the 8051 port pins, and transmits it out the RS-232 side through the MAX3221 driver. The 8051 simultaneously monitors its internal UART for incoming communications from the RS-232 side, and transmits this data out the IrDA side through the MAX3100. The low-level routine (UTLK) is the core routine that sends and receives data over the port pins to simulate an SPI port on the 8051. This technique is useful for any 8051-based MAX3100 port-pin-interfaced application.

## SPI/MICROWIRE-Compatible UART in QSOP-16

Figure 10. Bidirectional RS-232 IrDA Using an 8051

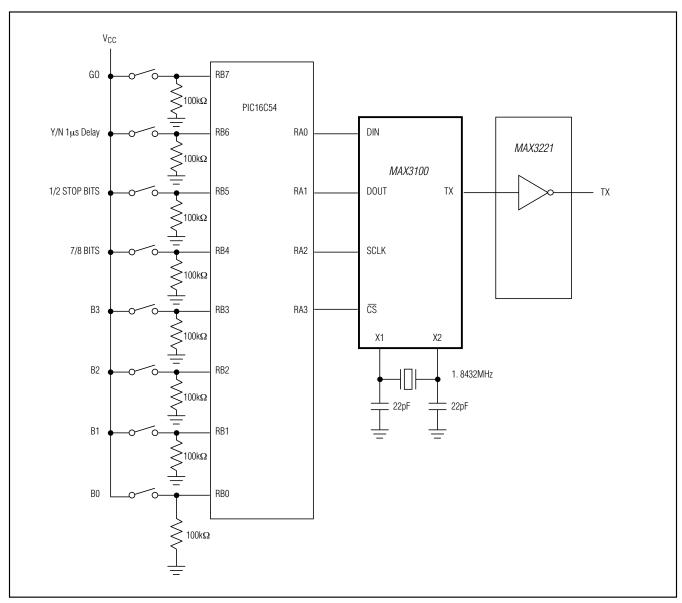

## Interface to PIC Processor ("Quick Brown Fox" Generator)

Figure 11 illustrates the use of the MAX3100 with the PIC®. This circuit is a "Quick Brown Fox" generator that repeatedly transmits "THE QUICK BROWN FOX JUMPS OVER THE LAZY DOG" (covering the entire alphabet) over an RS-232 link with adjustable baud rate, word length, and delay. Although a software-based UART could be implemented on the PIC, features like accurate variable baud rates, high baud rates, and simple protocol selection would be difficult to implement reliably. The 16C54 in the example is the most basic of the PICs. Thus, it is possible to implement the example on any member of the PIC family.

The software routine (Figure 12) begins by reading the DIP switch on port RB. The switch data includes 4 bits for the baud rate, 1 bit for number of stop bits, 1 bit for a word length of 7 or 8 bits, and 1 bit for delay between messages. The PIC reads the switch only at initialization (reset), and programs the parameters into the MAX3100. It then begins sending the message repeatedly. If the delay bit is set, it inserts a 1sec delay between transmissions. As in the 8051 example, the main routine is called UTLK, and can be used in any PIC-based, port-pin-interfaced application.

PIC is a registered trademark of Microchip Corporation.

# SPI/MICROWIRE-Compatible UART in QSOP-16

Figure 11. Quick Brown Fox Generator

## **SPI/MICROWIRE-Compatible UART in QSOP-16**

## \_MAX3100 Synchronous-to-Asynchronous SPI UART at a Glance

Table 9. Synchronous Data Input Format (DIN pin from microprocessor, SPI MOSI)

| Oner            |    | Bit Number |     |       |    |    |     |     |              |     |     |     |     |     |     |      |

|-----------------|----|------------|-----|-------|----|----|-----|-----|--------------|-----|-----|-----|-----|-----|-----|------|

| Oper-<br>ation  | 15 | 14         | 13  | 12    | 11 | 10 | 9   | 8   | 7            | 6   | 5   | 4   | 3   | 2   | 1   | 0    |

| Write<br>Config | 1  | 1          | FEN | SHDNi | TM | RM | РM  | RAM | IR<br>(IrDA) | ST  | PE  | L   | В3  | B2  | B1  | В0   |

| Read<br>Config  | 0  | 1          | 0   | 0     | 0  | 0  | 0   | 0   | 0            | 0   | 0   | 0   | 0   | 0   | 0   | TEST |

| Write<br>Data   | 1  | 0          | 0   | 0     | 0  | TE | RTS | Pt  | D7t          | D6t | D5t | D4t | D3t | D2t | D1t | D0t  |

| Read<br>Data    | 0  | 0          | 0   | 0     | 0  | 0  | 0   | 0   | 0            | 0   | 0   | 0   | 0   | 0   | 0   | 0    |

Table 10. Synchronous Data Output Format (DOUT pin to microprocessor, SPI MISO)

| 0===            |    | Bit Number |     |       |    |           |     |     |              |     |     |     |     |     |     |     |

|-----------------|----|------------|-----|-------|----|-----------|-----|-----|--------------|-----|-----|-----|-----|-----|-----|-----|

| Oper-<br>ation  | 15 | 14         | 13  | 12    | 11 | 10        | 9   | 8   | 7            | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| Write<br>Config | R  | Т          | 0   | 0     | 0  | 0         | 0   | 0   | 0            | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| Read<br>Config  | R  | Т          | FEN | SHDNo | TM | RM        | PM  | RAM | IR<br>(IrDA) | ST  | PE  | L   | В3  | B2  | B1  | В0  |

| Write<br>Data   | R  | Т          | 0   | 0     | 0  | RA/<br>FE | CTS | Pr  | D7r          | D6r | D5r | D4r | D3r | D2r | D1r | D0r |

| Read<br>Data    | R  | Т          | 0   | 0     | 0  | RA/<br>FE | CTS | Pr  | D7r          | D6r | D5r | D4r | D3r | D2r | D1r | D0r |

Table 11. Bit Definitions\*

| Register | Bit<br>Name | Bit Set (1)                             | Bit Clear (0)                          |

|----------|-------------|-----------------------------------------|----------------------------------------|

| Config   | FEN         | Disable FIFO buffer                     | Enable FIFO<br>buffer                  |

| Config   | SHDNi       | Shutdown                                | Operate                                |

| Config   | TM          | Enable transmit-<br>done interrupt      | Disable transmit-<br>done interrupt    |

| Config   | RM          | Enable data-<br>received inter-<br>rupt | Disable data-<br>received<br>interrupt |

| Config   | РM          | Enable parity interrupt                 | Disable parity interrupt               |

| Config   | RAM         | Enable framing-<br>error interrupt      | Disable framing-<br>error interrupt    |

| Config   | IR          | Enable IrDA timing mode                 | Standard<br>timing                     |

| Config   | ST          | Two stop bits                           | One stop bit                           |

| Config   | PE          | Parity enabled                          | Parity disabled                        |

| Register      | Bit<br>Name | Bit Set (1)                   | Bit Clear (0)                  |

|---------------|-------------|-------------------------------|--------------------------------|

| Config        | L           | Word length = 7 bits          | Word length = 8 bits           |

| Write<br>Data | TE          | Inhibit TX output             | Enable normal operation        |

| Write<br>Data | RTS         | Drive RTS output pin low      | Drive RTS out-<br>put pin high |

| Write<br>Data | Pt          | Transmit parity = 1           | Transmit parity = 0            |

| Read<br>Data  | RA/FE       | Data overrun or framing error | Normal                         |

| Read<br>Data  | CTS         | CTS input pin is low          | CTS input pin is high          |

| All           | R           | Data has been received        | Data buffer is empty           |

| All           | Т           | Transmit buffer is empty      | UART is busy transmitting      |

**Table 12. Field Definitions**

| Register   | Field Name | Meaning             |  |  |

|------------|------------|---------------------|--|--|

| Config     | B3-B0      | Baud-rate divisor   |  |  |

| Write Data | D7t-D0t    | Transmit data       |  |  |

| Read Data  | Pr         | Received parity bit |  |  |

| Read Data  | D7r–D0r    | Received data       |  |  |

Table 13. 1.8432MHz Baud Rates

| B3B0    | BRD | Baud   | B3B0    | BRD | Baud  |

|---------|-----|--------|---------|-----|-------|

| 0 0 0 0 | 1   | 115.2k | 1000    | 3   | 38.4k |

| 0 0 0 1 | 2   | 56k    | 1 0 0 1 | 6   | 19.2k |

| 0 0 1 0 | 4   | 28k    | 1 0 1 0 | 12  | 9600  |

| 0 0 1 1 | 8   | 14k    | 1 0 1 1 | 24  | 4800  |

| 0 1 0 0 | 16  | 7200   | 1 1 0 0 | 48  | 2400  |

| 0 1 0 1 | 32  | 3600   | 1 1 0 1 | 96  | 1200  |

| 0 1 1 0 | 64  | 1800   | 1 1 1 0 | 192 | 600   |

| 0 1 1 1 | 128 | 900    | 1 1 1 1 | 384 | 300   |

<sup>\*</sup>Default setting is clear

## SPI/MICROWIRE-Compatible UART in QSOP-16

```

:IrDA CODE FOR MAX-3100 UART- 8051 based

CONSTANTS

PCON EQU 87H

PORT PIN DEFINITIONS- BIT BANGING IF

DOUT BIT P1.0 ;data out (from uart)

DIN BIT P1.1 ;data in (from UART)

SCLK BIT P1.2

serial clock

;chip select- act low

CS BIT P1.3

IRQ BIT P3.2

;(irq) polled in this code

RAM LOCATIONS

TX1 EQU 10H

transmit regs;

TX2 EQU 11H

RX1 EQU 12H

receive regs;

RX2 EQU 13H

ORG

OH

BEGIN: MOV SP,#70H

;initialize stack

CLR SCLK

;clear sclk - normally low

initialize 8051 internal uart

MOV TMOD, #20H ;t1 baud

/reload value baud 960

MOV SCON,#50H /uart- m1, tx and rx

MOV PCON,#80H /double baud rate bit

MOV TCON,#40H /start baud fire

;reload value baud 9600/xtal 5.5M

initialize max3100 uart- irda mode at 9600 baud

MOV TX1,#0E4H ;high byte of config~ R ints

MOV TX2,#0CAh ;9600 baud irda mode and two stops

CALL UTLK ;send to uart- write config

LOOP: JNB IRQ,URCV ;data avail from 3100 uart?

NRECV: JBC RI,RCV51

;check for 8051 rcv- tx out irda

JMP LOOP

hang here forever;

byte recieved from 3100 wart- get it and send out 8051 wart

; send out on RS-232 side 9600 baud

;byte recieved from 8051 wart- get it and send out 3100 wart

RCV51: MOV A, open

MOV TX1,#80H /tx data

MOV TX2,A /data to irda

CALL UTLK /send to uart-

TO TOOP /back to top

; send to wart- send data out IrDA

SUBROUTINES

; UTLK- talk to wart- main routine

send 16 bits from TX1 TX2 and rcv 16 to RX1 RX2

UTLK: CLR CS

:activate cs

MOV A, TX1

get high byte

; send out

; get received 1

; get high byte

; send out

CALL BYT8

MOV RX1,A

MOV A, TX2

CALL BYT8

MOV RX2,A

get received 2

SETB CS

set CS high

DONE

;********

; BYT8- shift out & in 8 bits with spi clocking- from and to acc

BYT8:

MOV R4,#8

:8 bits to send

make sure din is input

SETB DIN

B8LP: RLC A

get msb of acc to carry

MOV

DOUT,C ;put out on pin

SETB SCLK

;clock high;get data after clk high;clock low

;clock high- clock

MOV C,DIN

CLR SCLK

MOV ACC.0,C

;put in lsbit of a

;loop til 8 bits

DJNZ R4,B8LP

RET

; end of code

```

Figure 12a. 8051 IrDA/RS-232 Code

```

; MAX-3100 UART WITH PIC "QUICK BROWN FOX GENERATOR CODE"

DEVICE PIC16C54,XT_OSC,WDT_OFF,PROTECT_OFF

:RAM LOCATIONS

;data to uart byte 1

TX1

EOU

TX2

EQU

11H

data to wart byte 2

;data from uart byte 1

RX2

EQU

13h

;data from uart byte 2

LPCNT

14H

EOU

;loop counter

;shift out temp variable

SHFTO

EQU

SHFTI

EQU

16H

;shift in temp variable

DLVAL

EOU

17H

delay value;

;temp variable

;temp variable

TEMP

EOU

18H

GP1

EOU

19H

GP2

EQU

1AH

;temp variable

CHPTR

;character pointer

; constants/literals

Су

EQU

0

;carry bit

EOU

zero bit

; i/o equates

:uart connected to pic on port RA

;data out (to uart)

DOUT

EOU

0

DIN

EQU

;data in (from uart)

EQU

serial clock

EQU

;chip select- act low

:Configuration dip switch connected to RB

RBO to RB3 are baud rate BO-B3

RB4 is 7 or 8 data bits

RB5 is 1/2 stop bits

RB6 is speed of sending about 100cps or 2.5 cps

RB7 is run/stop

note configuration bits are only read on reset

; subroutine area- pic must have these in low memory

;UART SERIAL (SPI) support routines

; send 16 bits from tx1 and tx2, receive 16 to rx1 and rx2

BCF

RA,CS

;activate cs

MOVE

TX1,0 ;get tx1 to w

send byte 1, recieve byte 1

CALL

BYT8

stash byte 1

MOVF

;get tx1 to w

BYT8

CALL

; send byte 1, recieve byte 1

MOVWF

RX2

stash byte 1

RA.CS

BSF

;activate cs

RETLW

;all done

;LOCAL SUB FOR SHIFTING IN/OUT 8 BITS- CORE OF SPI SUPPORT

; BYT8- shift out/in 8 bits w/spi- from and to w, temp shfti,shfto

BYT8

MOVWF

SHFTO ;put in shift out

MOVLW

8

;load loop counter

LPCNT

MOVWF

stash it

RLF

SHFTO,1

;get high bit to send

BCF

;preclear dout

STATUS, CY

BTFSC

;if in low then skip

BSF

RA, DOUT

set dout

BSF

RA, SCLK

;clock high- clock out/get input

STATUS, CY

preclear carry

BTFSC

RA,DIN

;if in low then skip

BSF

STATUS, CY

;set carry

RLF

SHFTI,1

rotate into place- shfti;

;clock low

BCF

RA, SCLK

DECFSZ LPCNT,1

;do loop counter

GOTO

B8LP

;loop til 8

MOVE

SHFTI,0

;put shfto to w- result

0

RETLW

end spi serial support

```

Figure 12b. MAX3100 Using PIC μC

## SPI/MICROWIRE-Compatible UART in QSOP-16

```

delay routine- counts down dlval (loaded at init)

;load delay

DELAY

MOVF

DLVAL,0

MOVWF

DLY2X

GP2

;put it in

DLLP2

CLRF

GP1

;use gpl to count off ticks

GP1 ; use gp1 to count off ticks

GP1,1 ; dec gp1 value til 10 ms

DLLP1 ; just loop

GP2,1 ; dec gp2 value

DLLP2 ; do another 10 ms til gp2=0

DECFSZ GP1,1

GOTO

DECFSZ GP2,1

GOTO

;return

this "subroutine" returns literal of pc+chptr

this is the only way to pull out rom literals on the pic...

MOVF

CHPTR, W

GET IN W

ADDWF

JUMP TO TABLE

QUICK BROWN FOX MESSAGE

RETLW "THE QUICK BROWN FOX JUMPS OVER THE LAZY DOG"

The above sentence needs a single line for a single letter or space ie. RETLW

; carriage return

RETLW

ODH

0AH

RETLW

;line feed

RETLW

end of message

MAIN ROUTINE-

MOVLW OFFH

;all of rb is input- dip switch

W.TVOM

08

;init port a with cs high only

output to port register; ra is output except din

MOVWF

RA

02H

MOVLW

;ra is output except din

;set it- now has

;no wdt- rtcc from clock

TRIS

OPTION

;put in option register

read switches and bit twiddle to configure uart- tx2 (1s byte)

get port b to w

RB,0

;and for 1 and b0-b3

MOVWF

stash in tx2;

BSF

BTFSC

RB,5

BCF

MOVLW

BTFSS

MOVIW

MOVWF

MOVLW

MOVWF

;send to uart- configured

uart is now configured as set on dip switch

:**** MATN 1.00P ****

go must stay high for run- else stop and reset string ptr

clear pointer with offset 1 cload pointer

MOVLW

HOLD

CHPTR

RB,7 ;wait high

HOLD ;go to reinit and hold

QBF ;get character to w

OFFH ;check for end of mess:

HANG

BTFSS

JMP

CALL

ANDLW

;check for end of message (zero)

STATUS, Zr

BTFSC

;bail

HOLD

GOTO

;bail to reinit pointer

MOVWF

TX2

;load data to tx2

MOVLW

080H

;write data

MOVWF

TX1

;put in place

CALL

UTLK

;send it

INCF

next character;

CALL

;delay

JMP

HANG

:***************

; VECTORS- start

ORG

1FFH

reset vector

```

Figure 12b. MAX3100 Using PIC μC (continued)

# SPI/MICROWIRE-Compatible UART in QSOP-16

### Typical Operating Circuit

## **Chip Information**

PROCESS: BiCMOS

SUBSTRATE CONNECTED TO GND

### \_Package Information

For the latest package outline information and land patterns, go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.

| PACKAGE TYPE   | PACKAGE CODE | DOCUMENT NO.   |

|----------------|--------------|----------------|

| 14 Plastic DIP | P14-3        | <u>21-0043</u> |

| 16 QSOP        | E16-1        | <u>21-0055</u> |

| 24 TQFN-EP     | T2444-4      | <u>21-0139</u> |

## **SPI/MICROWIRE-Compatible UART in QSOP-16**

### **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION               | PAGES<br>CHANGED |

|--------------------|------------------|---------------------------|------------------|

| 1                  | 12/01            | Changed pin labeling      | 17               |

| 2                  | 1/09             | Added 24 TQFN information | 1, 2, 5, 24      |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.